When talking about the upgrade in design boundaries, 224G PAM4 marks a shift as it operates under entirely new electrical and layout constraints. Signal edge rates and timing margins are tight enough that even minor layout decisions affect system performance.

Every stackup, via, and routing rule must hold under actual load conditions. Teams entering this space often find that what worked at 112G no longer scales. Crosstalk, loss, and power noise surface faster. What looked like clean routing becomes a source of reflection.

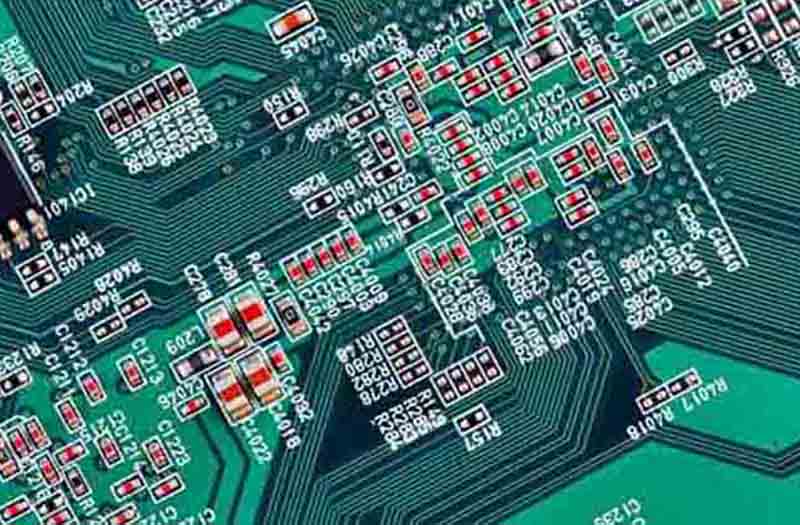

One engineer described it as threading a needle through a moving train. It’s not enough to get the layout done, but it has to hold at speed. This article walks through the challenges engineers face while designing a 224G PAM4 pcb circuit board. From signal modeling to manufacturing and thermal planning, every piece matters. Whether you’re working on a circuit board prototype or scaling a high-density interconnect, execution will drive the results.

High-Speed PCB Design Considerations

A design team re-used their 112G layout strategy for a new 224G PAM4 switch card. It failed in the lab. Timing skew and via reflection wiped out the eye margin. They underestimated how much less room 224G allows for error. At this level, the pcb circuit board becomes part of the signal path. This all must be modeled and controlled:

- Trace geometry

- Via stub length

- Layer spacing

There’s no safety net. Impedance must hold tight across transitions. That means careful stackup planning, tuned return paths, and backdrilled vias. Even connector breakout zones need rework. One layout shift or stub longer than 10 mils can cause eye closure. For any circuit board operating at 224G, copper geometry isn’t abstract. It’s a measurable delay and distortion. Teams building high-density interconnect boards for AI, networking, and storage must treat layout as signal routing and not just physical placement. Otherwise, the board fails before power is applied.

Signal Integrity and Simulation

At 224G PAM4, simulation isn’t optional. One company learned this when its hardware passed DC and low-speed checks but failed compliance testing. Their mistake was relying on layout rules without validating return paths, stub effects, or mode conversion. The signal didn’t degrade; it collapsed.

Accurate modeling helps expose weak links before fabrication. Use 3D full-wave solvers to simulate vias, breakouts, and stackup transitions. Time domain analysis still helps, but frequency-domain S-parameters become more useful at these rates. Make sure return loss and insertion loss match real-world conditions.

One engineer simulated a via field that looked clean in 2D tools but caused mode conversion at 28 GHz in full simulation. That caused timing mismatches across a high-density interconnect lane set. Start with stackup, simulate path by path, then validate the entire pcb circuit board model. A working circuit board layout is no guarantee. Only tested signal behavior matters at this speed.

PCB Materials and Manufacturing

A hardware vendor switched to a cheaper prepreg for a 224G build to save cost. The test boards failed during eye diagram validation. Postmortem showed the resin system couldn’t handle the loss profile above 40 GHz. The material absorbed too much signal power.

At 224G PAM4, dielectric loss becomes a dominant factor. Use low-Df laminates with tight process control. Materials like Tachyon 100G or Megtron 7 are common. However, it’s not just about material choice. It’s about:

- Consistency during drilling

- Lamination

- Plating

Poor registration or drill wander ruins via impedance. In one batch, poor backdrill alignment caused signal reflection across every differential pair in a circuit board spine. That’s not a layout issue, but a fabrication failure. Always partner with shops that have experience producing high-density interconnect builds for 50 GHz+ systems. The best pcb circuit board design means little if your fabrication is unable to hold the process tight enough.

Interconnect Design and Optimization

At 224G PAM4, every interconnect behaves like a tuned circuit. One design team tried using standard breakout geometries for a QSFP-DD module. During testing, reflection peaks hit 35 GHz. The launch region geometry caused a mismatch that couldn’t be equalized out. They had to rework the footprint and retune the via structure.

Think of the interconnect as a pressure valve. If it’s misaligned, the whole system backs up. Every trace from ASIC to connector must be impedance-matched and phase-aligned. That includes tuning the breakout region, reducing stub length, and managing reference plane transitions.

In high-density interconnect designs, routing around dense connector cages makes this harder. One team switched to embedded vias to shorten launch paths and remove resonance near 40 GHz. That allowed their pcb circuit board to pass compliance with margin. Don’t assume the connector works by default. It’s part of the signal chain, just like the circuit board trace.

Compliance and Industry Standards

A vendor submitted a 224G PAM4 board for OIF-CEI compliance. Lab measurements showed clean signals at 25°C but severe eye collapse at 70°C. Their issue wasn’t the layout. It was a failure to test across the full compliance range. Standards for 224G cover:

- Jitter

- Loss

- Crosstalk

- Equalization under thermal and voltage stress

Compliance testing also checks long trace channels, short channels, and backplane equivalents. One pcb circuit board passed early lab tests but failed OIF-CEI margin at insertion loss limits due to minor via mismatches. That error came from using relaxed drill specifications on a dense high-density interconnect backplane. Standards reflect real-world operating conditions, not lab conditions.

Always simulate, then validate, using reference setups that match OIF-CEI or IEEE guidelines. If a circuit board fails late in the process, the cost isn’t just time. It affects product launch and customer trust. Testing early conditions is the only safe path.

Power Integrity and Thermal Management

A networking OEM built a 224G line card with tight routing but underestimated VRM placement and copper balancing. During thermal soak testing, power noise spiked on the 0.85V rail, causing link flaps across multiple lanes. At this speed, power delivery behaves like a signal path. Ripple, bounce, and heat all affect the eye margin.

Think of power rails as highways with fast-moving traffic. If the lanes are narrow or full of potholes, everything slows down or crashes. Decoupling must be targeted and compact. Planes must be low-inductance and wide enough to support transient demand. Thermal planning goes hand in hand with layout.

One pcb circuit board using stacked ASICs failed thermal tests due to poor airflow design. Heat built up near the high-density interconnect region, warping the core and shifting impedance. Power and heat issues often show up late. Once they do, there’s no fix unless the circuit board is redesigned from scratch.

Optical and Co-Packaged Solutions

A hyperscale team transitioned from copper to co-packaged optics on their 224G PAM4 switch cards. They struggled at first. Optical modules were clean, but the electrical interface between ASIC and optics introduced unexpected reflections. The copper traces were short, but not short enough.

Co-packaged optics eliminate long copper runs but magnify layout precision. Think of it like building a bridge between two floating docks. The shorter the span, the more precise the connection needs to be. One pcb circuit board had to be respun to adjust stub lengths and change the pitch of breakout traces. The switch helped reduce insertion loss, but only after tight coordination between packaging, layout, and simulation teams.

For high-density interconnect designs with integrated optics, even 3D stacking and microvias must be tuned to match optical module impedance. If the circuit board isn’t designed as part of the optical system, the benefit of co-packaging gets lost in transition.

Next-Generation Technologies and Future Trends

A research lab prototyped a 448G PAM4 test platform using a hybrid substrate with integrated passives. It worked, but only after three iterations and multiple co-design sessions. That’s where 224G design is heading. More integration, less margin. Substrates may shift from standard FR-4 to low-loss hybrid cores or glass-based builds.

Active thermal control, embedded optics, and silicon photonics are no longer outliers. Think of the pcb circuit board as moving from a wiring platform to a complete electrical package. Every trace, via, and copper pour becomes part of a tuned machine. High-density interconnect will include optical layers and AI accelerators.

Early adopters are already testing chiplet-based circuit board designs where packaging, power, and signal need a single plan. The next wave won’t be faster versions of old boards. It’ll be tightly engineered platforms, where every layer talks to every other.

Conclusion

224G PAM4 design is a shift in how pcb circuit board projects are planned, simulated, built, and validated.

If you’re working on high-speed circuit board development or stepping into high-density interconnect layout, Benchuang simplifies the process. Use their online price submit option for instant quotes on HDI, RF, Flex, Rigid-Flex, Quick Turn, Prototypes, and full PCB Assembly.

![Understanding PCB Costs & Pricing [Your Complete Guide] Understanding PCB Costs & Pricing [Your Complete Guide]](https://hdicircuitboard.com/wp-content/uploads/elementor/thumbs/Understanding-PCB-Costs-Pricing-Your-Complete-Guide-qzzhe6mcaxuolkux3xalfktgavumi9y1aqfbs9bpv4.webp)