How to Design HDI Microvia PCB: A Technical Blueprint for High-Density Interconnect Excellence

Material Selection

- Dielectric materials must align with laser drilling compatibility and thermal stability requirements for HDI PCB and microvia applications

- Recommended options: Isola FR408HR, FR370HR, I-Speed, Nelco N7000-2HT, Rogers RO4003, RO4350, and PTFE-based laminates for RF PCB

- Key properties for selection:

- Glass transition temperature (Tg) ≥200°C for thermal endurance in multilayer PCB

- Low dielectric constant (Dk) for signal integrity in high-speed HDI circuit boards

- Uniform thickness (60-100µm) to ensure consistent microvia formation

- Laser-drillable resin systems with flat or spread glass structures (1035, 1067, 1086)

- Compatibility with sequential lamination cycles for rigid flex pcb manufacturing

- Non-reinforced build-up films (e.g., ABF) for advanced HDI PCB to achieve low z-axis expansion

- Material pairing considerations: Match thermal expansion coefficients (CTE) to minimize microvia stress

Learn more about: What is a HDI Microvia PCB

Microvia Type

| Microvia Type | Definition | Applications | Reliability | Space Efficiency |

|---|---|---|---|---|

| Blind Via | Connects outer layer to internal layers without full board penetration | Multilayer PCB, RF PCB, flexible printed circuit | High (with aspect ratio ≤0.8:1) | Medium-High |

| Buried Via | Internal layer connections only, no surface exposure | Dense multilayer PCB, HDI circuit boards | High (when limited to 2-layer stacks) | High |

| Stacked Microvia | Vertical alignment of blind/buried vias across layers | Fine-pitch BGAs, compact HDI PCB | Moderate (risk of voids) | Highest |

| Staggered Microvia | Offset arrangement across layers | Thermal cycling environments, rigid flex pcb | Highest | Medium |

| Skip Via | Connects non-consecutive layers (e.g., 1-3) | Reduced lamination needs, cost-sensitive HDI PCB | High | Medium |

- Selection criteria based on:

- Routing density requirements for high-density interconnect designs

- Thermal cycle exposure (staggered preferred for ≥100 cycles)

- Layer count (stacked optimal for 3+ layer HDI circuit boards)

- Space constraints (stacked saves 30-40% space vs. staggered)

Aspect Ratio

- Optimal range: ≤0.8:1 for microvia reliability in HDI PCB (0.64:1-0.75:1 preferred)

- Maximum allowable: 1:1 per IPC-T-50M standards for multilayer PCB

- Calculation: Aspect Ratio = Drill Depth ÷ Microvia Diameter

- Impact of non-compliance:

- Aspect ratio >1:1 increases plating voids by 40%+

- Thin copper plating at via bottoms (failure initiation point)

- Poor thermal stress resistance in flexible pcb applications

- Dielectric thickness correlation:

- 3mil dielectric → 3.9-4mil drill size (1.3x ratio)

- 60-80µm dielectric → 80-100µm microvia diameter

- Adjustments for application:

- RF PCB: Tighter aspect ratio (≤0.7:1) for signal integrity

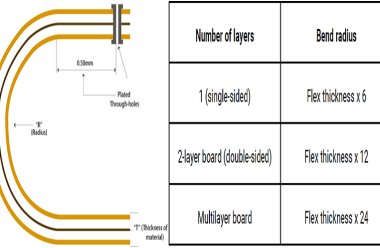

- Flexible pcb: Lower aspect ratio (≤0.6:1) for bend durability

Pad & Spacing

- Capture pad dimensions:

- Class 2: 325µm (recommended), 250µm (advanced)

- Class 3: 350µm (recommended), 250µm (advanced)

- Target pad requirements:

- Minimum diameter = 80% of microvia diameter

- Class 2: 300µm (recommended), 250µm (advanced)

- Class 3: 325µm (recommended), 250µm (advanced)

- Spacing specifications for HDI circuit boards:

- Microvia to PTH edge: 380µm (recommended), 300µm (advanced)

- Outer layer microvia spacing: 100µm (recommended), 76µm (advanced)

- Inner layer microvia spacing: 100µm (recommended), 76µm (advanced)

- Staggered microvia pitch: 400µm (recommended), 225µm (advanced)

- Solder mask clearance: 0mil to prevent solder bridging in microvia

- Annular ring minimums:

- External layers: ≥2mil (Class 3)

- Internal layers: ≥1mil (Class 3)

- HDI PCB optimized: 0.1mm for space efficiency

Copper Fill & Plating

- Copper fill requirements:

- Void-free filling for stacked microvia in multilayer PCB

- Minimum copper thickness: 18µm for reliable conductivity

- Non-conductive epoxy filling for via-in-pad applications

- Plating standards:

- Uniform coverage across microvia barrel (no thin spots)

- Compliance with IPC-6012 Class 3 for critical applications

- Electroless nickel immersion gold (ENIG) for fine-pitch solderability

- Electroless nickel electroless palladium immersion gold (ENEPIG) for enhanced shear strength

- Plating process controls:

- Throwing power optimization for aspect ratios >0.7:1

- Thermal cycle resistance testing (≥100 cycles)

- Resistance change limit: ≤5% during reflow

- Post-plating treatments:

- Surface planarization for stacked microvia

- Conductive cap for filled microvia in rigid flex pcb

Design Strategies

- Prioritize staggered microvia over stacked to reduce thermal stress accumulation

- Implement via-in-pad routing for fine-pitch BGAs (0.8mm pitch and below)

- Use skip vias for non-consecutive layer connections (avoids extra lamination)

- Limit stacked microvia to 2 layers maximum for reliability

- Separate microvia holes from dry film for effective laser ablation

- Optimize routing with dogbone structures for non-fine-pitch components

- Balance microvia density with thermal management needs in RF PCB

- Implement positive etchback per IPC-6012 Class 3 for military/aerospace applications

- Design symmetrical stack-ups to minimize warpage in multilayer PCB

- Use non-reinforced dielectrics (1mil thickness) for ultra-thin flexible printed circuit

Manufacturing & Testing

- Production process controls:

- Laser direct imaging (LDI) for fine-feature accuracy

- Class 100 cleanroom environment to prevent contamination

- Sequential build-up (SBU) for complex HDI circuit boards

- Semi-sequential build-up (SSBU) for testable substructures

- In-process inspections:

- Automated optical inspection (AOI) for microvia alignment

- X-ray inspection for void detection in copper fill

- Cross-sectional analysis for plating thickness verification

- Manufacturing tolerances:

- Mask registration: ±2-4mil

- Microvia diameter: ±1mil

- Layer alignment: ±1mil for Class 3

- Production timeframes: Standard 4 working days for basic HDI PCB

- Cost optimization: Limit filled microvia to external layers only

Laser Drilling

- Primary method for microvia ≤6mil diameter

- Drill size range: 40-150µm (4-6mil)

- Process parameters:

- Laser energy calibration for dielectric type

- Depth control accuracy: ±5µm

- Ablation rate matching to material properties

- Advantages over mechanical drilling:

- Precise depth control for blind via

- No drill bit breakage risk for small diameters

- Better hole quality for non-reinforced materials

- Laser drilling optimization:

- Homogeneous stack-up to prevent uneven heating

- Material-specific laser settings (resin vs. glass)

- Post-drilling cleaning to remove debris

- Limitations: Not suitable for skip vias requiring layer 2 capture pad penetration

IPC Compliance

- Mandatory standards for HDI microvia design:

- IPC-T-50M: Defines microvia geometry (max 1:1 aspect ratio, 6mil diameter limit)

- IPC-2226: Specifies stack-up configurations (Types I, II, III)

- IPC-6012D: HDI PCB performance requirements (drills ≤0.15mm, track width ≤0.1mm)

- IPC-TM-650 2.6.27: Thermal stress testing (6 reflow cycles at 230°C/260°C)

- IPC-TM-650 2.6.7.2: Thermal shock testing (-55°C to 210°C, 100 cycles)

- Class 3 compliance for critical applications:

- MIL-PRF-55110: Rigid PCB military standard

- MIL-PRF-31032: Performance and conformance requirements

- AS9100D: Aerospace quality management

- Documentation requirements:

- Certificate of conformance

- First article inspection report

- Ionic cleanliness test report

- Reflow profile documentation

Fabricator Collaboration

- Pre-design alignment:

- Confirm manufacturing capabilities (minimum microvia size, aspect ratio limits)

- Review stack-up feasibility for complex HDI circuit boards

- Validate material compatibility with production processes

- Design file requirements:

- Gerber, ODB++, or IPC-2581 format

- Clear DFM specifications for microvia

- Test coupon placement instructions

- Communication protocols:

- Fab notes detailing etchback requirements

- Microvia test method specifications

- Tolerance expectations for critical dimensions

- Collaboration milestones:

- Stack-up approval before layout finalization

- Prototype review for microvia reliability

- Production process validation for high-volume runs

Testing

- Microvia reliability tests:

- D-coupon testing (per IPC-2221 Appendix A/B)

- Resistance monitoring during thermal cycling

- Thermal shock testing (-55°C to 210°C)

- Reflow cycle testing (6 cycles minimum)

- Electrical performance tests:

- 4-wire resistance measurement

- Signal integrity analysis for RF PCB

- Controlled impedance verification

- Mechanical durability tests:

- Bend testing for flexible pcb

- Thermal cycling (≥100 cycles)

- Vibration and shock testing for aerospace applications

- Failure criteria:

- Resistance increase >5% = test failure

- Visible cracks in microvia barrel or pads

- Target pad pull-out or separation

- Copper voids exceeding 10% of via area

Design Considerations

- Application-specific adjustments:

- Aerospace: Tg ≥200°C, Class 3 compliance, staggered microvia

- Consumer electronics: Cost-optimized stack-up, via-in-pad

- RF PCB: Low Dk materials, controlled impedance microvia

- Flexible printed circuit: Thin dielectrics, low aspect ratio

- Trade-off management:

- Space vs. reliability (stacked vs. staggered microvia)

- Cost vs. performance (filled vs. non-filled microvia)

- Manufacturing complexity vs. design flexibility (via-in-pad vs. dogbone)

- Common design pitfalls to avoid:

- Aspect ratio exceeding 1:1 for microvia

- Insufficient pad size leading to stress concentration

- Incompatible material CTE leading to thermal failure

- Inadequate spacing causing signal interference

- Over-reliance on stacked microvia in high-temperature environments

Stack-Up

- IPC-2226 stack-up configurations:

- Type I: PTH + single microvia layer (one/both core sides)

- Type II: PTH + buried via + single microvia layer (one/both core sides)

- Type III: PTH + buried via + ≥2 microvia layers (one/both core sides)

- Type III Staggered: Staggered microvia + ≥2 layers

- Type III Capped: Filled/capped staggered microvia + dual PTH

- Stack-up optimization:

- Symmetrical layer count to prevent warpage

- Uniform material distribution for thermal stability

- Minimum dielectric thickness (60-80µm) for microvia

- Core thickness matching to microvia depth requirements

- Layer count considerations:

- 2+N+2 HDI stack-up for balanced performance

- Maximum microvia layers: 4 (for reliable manufacturing)

- Core layer count: 2-4 for rigid flex pcb

Thermal Management

- Thermal design elements:

- Material selection (high thermal conductivity laminates)

- Staggered microvia for improved heat dissipation

- Thin dielectrics (60-80µm) for thermal transfer

- HTg materials to withstand reflow temperatures

- Thermal stress mitigation:

- Matching CTE of adjacent materials

- Limiting lamination cycles to 3 maximum

- Avoiding stacked microvia on buried holes

- Optimizing microvia placement to distribute heat

- Reflow process controls:

- Peak temperature: 230°C or 260°C (per IPC-TM-650)

- Temperature ramp rate: Controlled to prevent thermal shock

- Preconditioning to stabilize microvia resistance

Space

- Space optimization techniques:

- Microvia diameter: 80-100µm (4-6mil) for HDI PCB

- Via pad size: 0.3mm (12mil) with 0.1mm annular ring

- Via-in-pad technology to save routing space

- Staggered microvia for dense layer connections

- Density improvements:

- 30-40% space savings vs. traditional through-hole vias

- Enables finer trace spacing (0.1mm standard)

- Supports fine-pitch BGAs (≤0.8mm pitch)

- Space vs. performance balance:

- Minimum microvia spacing: 220µm (advanced)

- Skip via for non-consecutive layers without extra space

- Balanced microvia density to prevent thermal hotspots

- Packaging benefits:

- Smaller overall PCB size (up to 50% reduction)

- Reduced layer count for equivalent functionality

- Enables miniaturization of rigid flex pcb and portable devices

HDI microvia design requires precise integration of material science, manufacturing processes, and design principles to create reliable, high-performance circuit board solutions. By adhering to IPC standards, optimizing material selection, and implementing proper design strategies, engineers can develop HDI PCB, rigid flex pcb, and flexible printed circuit designs that meet the demanding requirements of modern electronics. The careful balance of space efficiency, thermal management, and manufacturing feasibility ensures microvia reliability in applications ranging from consumer devices to aerospace systems.

![Understanding PCB Costs & Pricing [Your Complete Guide] Understanding PCB Costs & Pricing [Your Complete Guide]](https://hdicircuitboard.com/wp-content/uploads/elementor/thumbs/Understanding-PCB-Costs-Pricing-Your-Complete-Guide-qzzhe6mcaxuolkux3xalfktgavumi9y1aqfbs9bpv4.webp)