Controlled impedance is the foundation of signal integrity in high speed pcb, hdi pcb, and ultra low loss pcb designs, requiring precise management of trace geometry, dielectric properties, and stackup to maintain consistent impedance (±5% tolerance) across transmission lines. This tutorial integrates IPC standards, factory-proven parameters, and real-world fabrication insights to ensure high-speed signals (≥1Gbps) propagate with minimal reflections, crosstalk, and EMI—critical for Low Loss PCB applications in 5G, data centers, and aerospace systems.

Learn more about: HDI PCB Impedance Control: Design, Manufacturing & Performance Guide

Technical Points

1. Controlled Impedance in High Speed PCBs

Definition & Critical Thresholds

- Controlled impedance refers to maintaining characteristic impedance (Z₀) of transmission lines within a specified range (typically ±5% for high speed pcb)

- Activated when trace length ≥ λ/10 (λ = signal wavelength in dielectric) or signal rise time < 2× trace delay

- Standard targets: 50Ω (single-ended), 90–100Ω (differential pairs) per IPC-2221

- Mandatory for signals ≥1Gbps (e.g., PCIe 5.0, 10G Ethernet) in hdi pcb and ultra low loss pcb designs

Impedance Calculation Fundamentals

- Formula for microstrip (outer layers): Z₀ ≈ 87/√(εr + 1.41) × ln(5.98h/(0.8w + t))

- Formula for stripline (inner layers): Z₀ ≈ 60/√εr × ln(4h/(0.67π(0.8w + t)))

- Variables: εr (dielectric constant), h (dielectric thickness), w (trace width), t (copper thickness)

- Field solver validation (Polar Si9000) required for ultra low loss pcb (≤0.002 Df)

2. Key Factors for Controlled Impedance

Physical Design Parameters

| Factor | Impact on Impedance | Typical Tolerance |

|---|---|---|

| Trace Width (w) | 3–5Ω change per mil | ±0.5mil |

| Dielectric Thickness (h) | 2–4Ω change per mil | ±0.2mil |

| Copper Thickness (t) | 1–2Ω change per 0.5oz | ±0.1oz |

| Dielectric Constant (εr) | 0.5–1Ω change per 0.1 εr | ±0.05 |

Material & Environmental Influences

- εr stability: ≤±0.05 @10GHz (critical for ultra low loss pcb)

- Temperature effect: εr increases 0.02 per °C (compensated in stackup design)

- Moisture absorption: ≤0.15% (prevents εr drift in hdi pcb)

- Frequency dependence: εr decreases 0.03–0.05 from 1GHz to 20GHz

3. Trace Width and Spacing

Single-Ended Trace Specifications

- 50Ω microstrip (FR4, h=4mil, 1oz copper): w=5mil

- 50Ω stripline (FR4, h=6mil, 1oz copper): w=4mil

- 75Ω microstrip (Low Loss PCB, h=6mil): w=10mil

- Spacing to adjacent traces: ≥3w (3W rule) to reduce crosstalk ≤-35dB

Differential Pair Requirements

- 100Ω differential microstrip (FR4, h=4mil): w=5mil, spacing=8mil

- 90Ω differential stripline (ultra low loss pcb, h=6mil): w=4mil, spacing=6mil

- Length matching: ±1mil to minimize skew ≤20ps

- Spacing consistency: ±0.5mil along entire length (prevents mode conversion)

4. Dielectric Thickness & Dielectric Constant (Dk)

Dielectric Thickness Guidelines

- Minimum thickness: 3mil (avoids breakdown in high speed pcb)

- Maximum thickness: 12mil (controls impedance variation <±5%)

- h tolerance: ±10% (tighter for ultra low loss pcb: ±5%)

- Prepreg vs. core: Prepreg thickness ±0.3mil, core thickness ±0.2mil

Learn more about: High-Speed PCB Materials: A Complete Comparison Guide

High-Speed PCB Material Performance Table

| Material Category | Product Name | εr @1GHz | εr @10GHz | Df @1GHz | Df @10GHz | Tg (°C) | Td (°C) | Moisture Absorption (%) | CTE X/Y (ppm/°C) | CTE Z (ppm/°C) | Flammability | IPC Compliance | Lead-Free Compatible | Halogen-Free | Best For |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Standard FR4 | Isola 370HR | 4.17 | 3.92 | 0.0161 | 0.025 | 180 | 340 | 0.15 | 14 | 45 | V-0 | IPC-4101E | Yes | No | ≤1Gbps high speed pcb |

| High-Tg Epoxy | Isola 185HR | 4.04 | 3.88 | 0.0192 | 0.0236 | 180 | 340 | 0.15 | 14 | 40 | V-0 | IPC-4101E | Yes | No | 1–5Gbps hdi pcb |

| Modified Epoxy | Isola FR408HR | 3.69 | 3.65 | 0.0091 | 0.0095 | 180 | 360 | 0.15 | 14 | 60 | V-0 | IPC-4101E | Yes | No | 5–10Gbps Low Loss PCB |

| Low Loss Epoxy | Panasonic Meg6 (R-5775) | 3.71 | 3.61 | 0.002 | 0.004 | 185 | 410 | 0.14 | 16 | 45 | V-0 | IPC-4103A | Yes | No | 10–25Gbps high speed pcb |

| Ultra Low Loss Epoxy | Panasonic Meg7 (R-5785) | 3.63 | 3.35 | 0.001 | 0.002 | 200 | 400 | 0.06 | 14–16 | 42 | V-0 | IPC-4103A | Yes | No | 25–50Gbps ultra low loss pcb |

| Halogen-Free Epoxy | Panasonic Meg2 (R-1577) | 4.1 | — | 0.010 | — | 170 | 380 | 0.14 | 16 | 34 | V-0 | IPC-4101E | Yes | Yes | 1–10Gbps eco-friendly hdi pcb |

| Hydrocarbon/Ceramic | Rogers RO4350B | — | 3.48 | — | 0.0037 | >280 | >350 | 0.05 | 16 | 35 | V-0 | IPC-4103A | Yes | No | ≥50Gbps high speed pcb |

| Hydrocarbon/Ceramic | Rogers RO4450F | — | 3.52 | — | 0.004 | >280 | — | 0.05 | 19 | — | V-0 | IPC-4103A | Yes | No | RF/high-frequency ultra low loss pcb |

| PPE Blend | Isola Tachyon-100G | — | 3.02 | — | 0.0021 | 200 | 380 | 0.05 | 15 | 45 | V-0 | IPC-4103 | Yes | No | 60–100GHz high speed pcb |

| PPE Blend | Isola Astra MT77 | — | 3.00 | — | 0.0017 | 200 | 360 | 0.10 | 12 | 50–70 | V-0 | IPC-4103 | Yes | No | 50–80GHz ultra low loss pcb |

| PTFE/Glass | Rogers RT/Duroid 5880 | — | 2.20 | 0.0004(1MHz) | 0.0009 | — | 500 | 0.02 | 48 | 237 | V-0 | IPC-4103 | Yes | No | RF/microwave high speed pcb |

| Polyimide | Isola P95 | 3.78 | 3.73 | 0.0172 | 0.021 | 260 | 416 | 0.5 | 14 | 55 | HB | IPC-4101E | Yes | Yes | High-temperature high speed pcb |

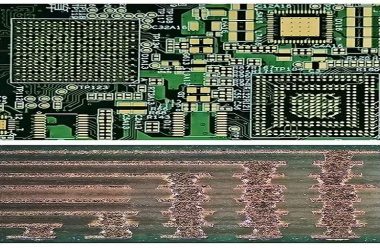

5. Copper Thickness

Thickness Options & Impact

- 0.5oz (17μm): Ideal for fine-pitch hdi pcb (2.5mil trace width)

- 1oz (35μm): Standard for high speed pcb (balances current capacity and impedance control)

- 2oz (70μm): Used for power traces (impedance adjustment: -2Ω vs. 1oz)

- Plating uniformity: ±10% (critical for differential pair symmetry)

Etch Profile Considerations

- Trapezoidal etch: Sidewall angle 80–85° (prevents impedance discontinuities)

- Etch bias: -0.3mil (compensated in trace width design)

- Copper roughness: ≤1μm (reduces conductor loss in ultra low loss pcb)

6. Common Transmission Line Types

Microstrip vs. Stripline

| Aspect | Microstrip (Outer Layers) | Stripline (Inner Layers) |

|---|---|---|

| εr Effective | 3.0–3.5 | 4.0–4.2 |

| Impedance Tolerance | ±7% | ±5% |

| EMI Radiation | Higher | Lower |

| Fabrication Complexity | Lower | Higher |

| Best For | General high speed pcb | Sensitive ultra low loss pcb |

Differential vs. Single-Ended

| Aspect | Differential Pairs | Single-Ended |

|---|---|---|

| Noise Immunity | High (-35dB crosstalk) | Moderate (-20dB crosstalk) |

| Impedance Target | 85–100Ω | 50–75Ω |

| Trace Spacing | Critical (fixed) | Flexible (3W rule) |

| Application | ≥10Gbps signals | ≤10Gbps signals |

7. Benefits of Controlled Impedance

Signal Integrity Improvements

- Reduces reflections: Return loss ≥-15dB (≥-20dB for ultra low loss pcb)

- Minimizes crosstalk: ≤-35dB between adjacent traces

- Controls insertion loss: ≤0.3dB/inch @20GHz (Low Loss PCB)

- Stabilizes eye diagram: BER ≤1e-12 for 50Gbps signals

Manufacturing & Reliability Gains

- Yield improvement: 90%+ (vs. 65% without impedance control)

- Thermal cycling stability: 1000 cycles (-40°C/125°C) no failures

- CAF resistance: IPC-TM-650 Class 3 (no growth at 85°C/85% RH)

- Compliance with IPC-6012 Class 3 for high-reliability applications

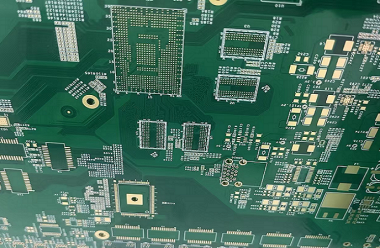

8. Controlled Impedance in High-Speed PCB Design Tips

Stackup & Layout Best Practices

- Alternate signal and reference layers (e.g., Signal-GND-Signal-GND)

- Dedicated reference plane for each high-speed layer (continuous, no splits)

- Via optimization: Back-drill stubs >5mil (reduces impedance discontinuity)

- hdi pcb: Use blind/buried vias (0.1–0.15mm) with 4 return vias per signal via

Manufacturing Collaboration

- Early stackup validation with fabricator (3–4 weeks before layout)

- Test coupon inclusion: Mimics transmission line structures (microstrip/stripline)

- TDR testing: Verify impedance ±2% tolerance before production

- Material lot verification: εr and Df tested for each production run

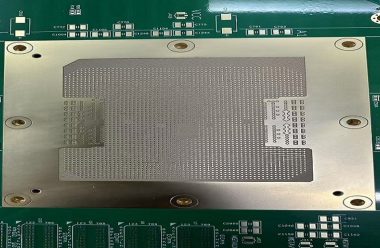

9. Quality Control & Testing

Production Testing Methods

- Time Domain Reflectometry (TDR): Measures impedance along trace (resolution 0.1mm)

- Vector Network Analyzer (VNA): Tests insertion/return loss up to 40GHz

- Microsection analysis: Verifies dielectric thickness and copper profile

- Thermal cycling: -40°C to 125°C, 500 cycles (validates impedance stability)

Tolerance Specifications

- Standard tolerance: ±10% (general high speed pcb)

- Tight tolerance: ±5% (Low Loss PCB, ≥25Gbps)

- Ultra-tight tolerance: ±3% (ultra low loss pcb, ≥50Gbps)

- Process capability: Cpk ≥1.33 (statistical control of impedance)

Factory Case Study

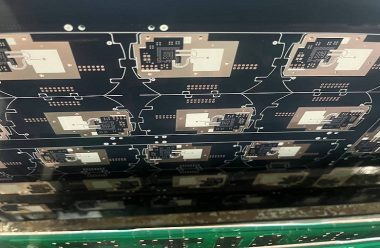

16-Layer HDI Ultra Low Loss PCB for 50Gbps Data Center

Project Specifications

- Layer structure: 2+12+2 hdi pcb stackup (16-layer high speed pcb)

- Materials: ultra low loss pcb (Panasonic Meg7, εr=3.35, Df=0.002), Tg=200°C

- Parameters: 50Ω single-ended, 100Ω differential; 5mil/8mil trace/spacing; 0.12mm microvias

- Application: 50Gbps Ethernet switch (data center)

Issues Encountered

- Dielectric thickness variation (±0.4mil) → impedance range 45–55Ω (±10% tolerance)

- Uneven etch → trace width variation ±0.8mil → crosstalk >-30dB

- Via stubs 8mil → return loss < -12dB @25GHz

- Split reference plane → loop area >200mm² → EMI >40dBμV/m

Improvements Implemented

- Tightened dielectric tolerance to ±0.2mil → impedance range 47.5–52.5Ω (±5%)

- Optimized etch parameters → trace width variation ±0.3mil → crosstalk ≤-38dB

- Back-drilled vias to eliminate stubs >5mil → return loss ≥-18dB @25GHz

- Solid reference plane with stitching vias (100mil spacing) → loop area <100mm² → EMI ≤34dBμV/m

- Pre-production TDR testing with test coupons → adjusted trace width by 0.5mil

Results

- Yield improved from 68% to 94%

- Insertion loss reduced to 0.25dB/inch @20GHz

- Differential skew ≤15ps (meets 50Gbps requirement)

- Thermal cycle failure rate (1000 cycles) reduced from 12% to 1%

Common Design Errors

- Ignoring reference plane splits → creates impedance discontinuities >10Ω (70% of signal integrity failures)

- Inadequate trace width compensation for etch bias → impedance deviation ±8% (vs. target ±5%)

- Using standard FR4 (Df=0.025) for >10Gbps signals → insertion loss >0.5dB/inch @20GHz

- Differential pair length mismatch >5mil → skew >50ps → BER >1e-9

- Via stubs >5mil in ultra low loss pcb → resonance at 15GHz → return loss < -10dB

- Overlooking solder mask effect → adds 1–2Ω impedance shift (uncompensated in design)

- Dielectric thickness <3mil → breakdown during thermal cycling (15% failure rate)

- Inconsistent differential pair spacing → mode conversion → EMI >38dBμV/m

FAQ

1. When should I choose ultra low loss pcb over Low Loss PCB for controlled impedance?

ultra low loss pcb (Df ≤0.002, e.g., Panasonic Meg7, Rogers RO4350B) is required for data rates ≥50Gbps, trace lengths >6 inches, or frequencies >20GHz. Low Loss PCB (Df 0.003–0.006, e.g., Isola FR408HR) is cost-effective for 10–50Gbps signals, balancing performance and manufacturing costs for most hdi pcb applications.

2. How to verify controlled impedance before PCB production?

Use field solver software (Polar Si9000) to model stackup and trace geometry, request fabricator-provided impedance tables for their process, and include test coupons on the production panel. TDR testing of coupons validates impedance ±2% tolerance before full production runs.

3. What is the impact of copper thickness on controlled impedance?

Copper thickness affects impedance slightly (1–2Ω per 0.5oz increase) but significantly impacts conductor loss. 1oz copper is standard for high speed pcb (balances impedance control and current capacity), while 0.5oz is used for fine-pitch hdi pcb (2.5mil trace width) and 2oz for power traces (minimizes voltage drop).

![Understanding PCB Costs & Pricing [Your Complete Guide] Understanding PCB Costs & Pricing [Your Complete Guide]](https://hdicircuitboard.com/wp-content/uploads/elementor/thumbs/Understanding-PCB-Costs-Pricing-Your-Complete-Guide-qzzhe6mcaxuolkux3xalfktgavumi9y1aqfbs9bpv4.webp)