High-speed PCB design for DDR5 and DDR6 requires ultra‑strict timing control, low‑loss materials, symmetric layer stackup, precision length matching, and robust power delivery to support 6.4Gbps–12.8Gbps data rates while maintaining signal integrity and low crosstalk. This guide delivers factory‑verified layout rules, material parameters, via management, and JEDEC‑compliant design practices for hdi pcb, Low Loss PCB, and high frequency pcb platforms.

Learn more about: What Is High-Speed PCB? A Comprehensive Guide

DDR5/DDR6 PCB Design Requires

Core Performance Mandates

- DDR5: 3.2–6.4Gbps data rate, 1.1V core voltage, 16n prefetch, BL16/BL32.

- DDR6: 6.4–12.8Gbps data rate, 0.9V core voltage, 32n prefetch, PAM4 signaling option.

- Timing skew: Intra‑byte lane ≤5ps (≤10mil); clock to strobe ≤20ps (≤40mil).

- Impedance stability: ±3% tolerance required for data rates above 6.4Gbps.

- Insertion loss: ≤0.25dB/inch @10GHz for DDR5; ≤0.15dB/inch @20GHz for DDR6.

Structural & Manufacturing Rules

- Minimum layer count: 8 layers for DDR5; 12 layers recommended for DDR6.

- Symmetric stackup required to limit warpage ≤0.2mm/m.

- Trace geometry: Width ±0.2mil, spacing ±0.2mil for controlled impedance.

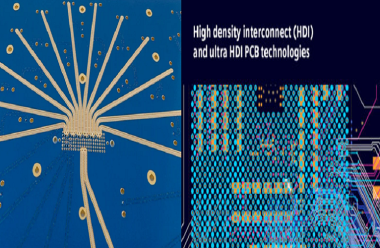

- hdi pcb support: 0.12–0.15mm microvias, stacked via capability, 2+N+2 structure.

Key Layout Guidelines for DDR5/DDR6

Topology and Routing

- Fly‑by topology mandatory for address/command/clock (A/C/C) lines.

- Point-to-point direct routing for data byte lanes (DQ/DQS/DBI).

- Maximum parallel run between different byte lanes: ≤200mil.

- Trace direction: Orthogonal transitions between layers to reduce broadside coupling.

- Bend rule: 45° only; radius ≥3× trace width; no 90° corners.

Layer Stackup

- Signal layers adjacent to solid ground planes; dielectric thickness 0.1–0.15mm.

- No adjacent signal layers; separate with ground or power planes.

- Power/ground plane pairs with tight spacing for high interplane capacitance.

- Stripline preferred for inner layers; microstrip allowed only for short outer traces.

- Total board thickness: 1.6mm ±0.1mm standard for server and AI accelerators.

Impedance Control

- Single‑ended (DQ/ADDR/CMD): 50Ω ±3% (DDR5/DDR6).

- Differential (CK/DQS): 100Ω ±3% (DDR5/DDR6).

- Reference plane: Continuous solid ground; no splits or gaps under traces.

- Etch compensation: Trapezoidal trace correction built into impedance calculation.

- Impedance test coupons mandatory on production panels (IPC‑6012 Class 3).

Learn more about : 50Ω / 75Ω / 100Ω Impedance in High Density Interconnect (HDI) PCBs: Design & Production Guide

Length Matching

- Byte lane internal skew: ≤5mil (≤2.5ps) for DDR5/DDR6.

- Clock to address/command: ±20ps skew (±40mil).

- DQS to DQ group: ±5mil matching within each byte lane.

- Fly‑by length progression: Controller → DRAM0 → DRAM1 → DRAM2 → DRAM3.

- Serpentine tuning: Pitch ≥5× trace width to avoid coupling.

Via Management

- Via type: Microvia 0.12–0.15mm for hdi pcb; avoid through‑hole vias on high‑speed lines.

- Via stub: ≤5mil for DDR6; ≤10mil for DDR5 (backdrilling required).

- Anti‑pad/pad/via: 10/20/40mil for 50Ω/100Ω impedance.

- Max vias per net: 1 via for DQ/DQS; 2 vias max for A/C/C.

- Ground shielding vias: 1mm pitch around critical differential pairs.

Decoupling

- 0201 MLCC capacitors: 0.1µF, 0.01µF, 0.001µF placed ≤2mm from BGA pads.

- Bulk capacitors: 10µF placed ≤5mm from power rail entry.

- Vias for capacitors: Dual vias, ≤0.2mm, direct to ground plane.

- Power plane isolation: Separate VDDQ/VPP domains to prevent noise coupling.

- Decoupling density: ≥8 capacitors per DRAM device.

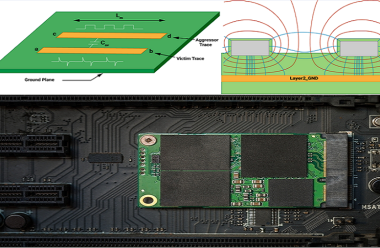

Crosstalk Mitigation

- 3W rule for DDR5; 5W rule for DDR6 (spacing ≥3×/5× trace width).

- Guard traces with grounded vias every 100–150mil in dense regions.

- Trace spacing: ≥4mil for 4mil width traces in hdi pcb designs.

- No parallel routing between clock and data lines.

- Intra‑pair spacing fixed; no necking or expansion.

DDR5/DDR6 Specific Considerations

Higher Speeds & Signaling

- DDR5 uses NRZ signaling; DDR6 supports PAM4 for doubled bandwidth.

- Equalization: DFE/FFE required for DDR6 long channels.

- Jitter budget: ≤30ps for DDR5; ≤15ps for DDR6.

- Eye height: ≥20mV for DDR5; ≥15mV for DDR6.

Power Delivery

- DDR5: 1.1V VDDQ; DDR6: 0.9V VDDQ with lower noise tolerance.

- Voltage ripple: ≤2% for DDR5; ≤1.5% for DDR6.

- On‑board PMIC for DDR5; dedicated power stage for DDR6.

- Plane capacitance: ≥150pF/cm² for high‑frequency noise suppression.

High-Speed PCB Material Selection

Material Grades

- Standard FR‑4: Df ≥0.015, not recommended for DDR5/DDR6.

- Low Loss PCB: Df 0.006–0.009, suitable for short DDR5 channels.

- High Frequency PCB: Df 0.003–0.005, required for DDR5 long channels & DDR6.

- Ultra‑low‑loss materials: Stable Dk ±0.1 over 1–20GHz.

Copper & Surface Finish

- Smooth copper or reverse‑treated foil (RTF) to reduce skin‑effect loss.

- Copper weight: 1oz (35µm) for signal layers; 2oz (70µm) for power planes.

- Surface finish: ENEPIG or immersion silver; avoid ENIG nickel loss.

- Glass weave: Low‑skew spread glass to minimize impedance variation.

Learn more about: High-Speed PCB Materials: A Complete Comparison Guide

Key Comparisons

| Parameter | DDR5 | DDR6 |

|---|---|---|

| Data Rate | 3.2–6.4Gbps | 6.4–12.8Gbps |

| Signaling | NRZ | NRZ + PAM4 |

| Voltage | 1.1V | 0.9V |

| Skew Tolerance | ±5ps (byte lane) | ±3ps (byte lane) |

| Impedance Tolerance | ±3% | ±2% |

| Recommended Material | Low Loss PCB | High Frequency PCB |

| Material Type | Df @10GHz | Max Data Rate | Application |

|---|---|---|---|

| Standard FR-4 | 0.018 | ≤3.2Gbps | Not Recommended |

| Low Loss PCB | 0.006–0.009 | ≤6.4Gbps | DDR5 Short |

| High Frequency PCB | 0.003–0.005 | ≤12.8Gbps | DDR5 Long / DDR6 |

Case Study: 12-Layer HDI High Frequency PCB

Project Specifications

- Layers: 12‑layer symmetric hdi pcb stackup.

- Protocol: DDR6 (8.0Gbps PAM4).

- Material: High frequency pcb (Df=0.0035, Dk=3.4).

- Impedance: 50Ω SE / 100Ω differential ±3%.

- Trace: 4.0mil width, 4.5mil spacing, stripline.

Issues Encountered

- Insertion loss: 0.32dB/inch @10GHz (exceeded 0.25dB limit).

- Crosstalk: –26dB (target ≤–35dB).

- Via stub: 18mil causing resonance and return loss degradation.

- Skew: 12ps inside byte lane (exceeded 5ps limit).

Improvements Implemented

- Upgraded from Low Loss PCB to high frequency pcb.

- Applied backdrilling to reduce stub from 18mil to 4mil.

- Increased trace spacing from 3.5mil to 7.5mil (5W rule).

- Length matching tightened to ±3mil; added serpentine tuning.

- Inserted ground guard traces with stitching vias every 120mil.

Results

- Insertion loss improved to 0.18dB/inch @10GHz.

- Crosstalk reduced to –36dB.

- Skew controlled to 2.8ps.

- Return loss improved to –24dB.

- Manufacturing yield increased from 74% to 96.2%.

| Case Study Aspect | Details / Parameters |

|---|---|

| Project Specifications | 12-layer symmetric HDI PCB, DDR6 (8.0Gbps PAM4), High Frequency PCB (Df=0.0035), 50Ω/100Ω, 4.0mil width, 4.5mil spacing |

| Issues Encountered | Insertion loss 0.32dB/inch @10GHz, crosstalk -26dB, via stub 18mil, skew 12ps (over 5ps limit) |

| Improvements Implemented | Upgraded to High Frequency PCB, backdrill stub 18→4mil, spacing 3.5→7.5mil (5W), matching ±3mil, guard traces with 120mil vias |

| Results | Insertion loss 0.18dB/inch, crosstalk -36dB, skew 2.8ps, return loss -24dB, yield 74%→96.2% |

Common Design Errors

- Inadequate Material Grade: Using standard FR‑4 or low‑loss material for DDR6 causes 30% excess loss and requires full redesign.

- Insufficient Length Matching: Skew >5ps in DDR6 byte lanes results in bit errors and unrepairable yield loss.

- Excessive Via Stub Length: Stubs >10mil create resonance that cannot be fixed after etching.

- Adjacent Signal Layers: Causes broadside crosstalk that increases noise by 200% and violates JEDEC limits.

Quality Control & Compliance

Testing Protocols

- TDR impedance measurement: 20ps rise time, 8‑point coupon test.

- S‑parameter test: Insertion loss, return loss, crosstalk up to 20GHz.

- Timing skew verification: Length audit with 0.1mil accuracy.

- Eye diagram test: At-speed validation with DDR6 test system.

Standards Compliance

- JEDEC JESD79‑5 (DDR5); JESD79‑6 (DDR6).

- IPC‑2221: Generic PCB design standard.

- IPC‑6012 Class 3: High‑performance reliability.

- IPC‑4103: High‑speed/high‑frequency laminate requirements.

FAQ

Q1: What material is required for DDR6 high speed pcb?

A1: DDR6 requires high frequency pcb with Df ≤0.005 and stable Dk up to 20GHz. Low Loss PCB is insufficient for 6.4Gbps+ operation.

Q2: What length matching tolerance is needed for DDR6?

A2: Intra‑byte lane skew must be ≤3ps (≤5mil). Clock to strobe must be ≤20ps (≤40mil). Tighter than DDR5 due to PAM4 sensitivity.

Q3: What via rules apply for DDR5/DDR6 in hdi pcb?

A3: Use 0.12–0.15mm microvias with backdrilling to ≤5mil stub for DDR6 and ≤10mil for DDR5. Max 1 via per data line.

Q4: What crosstalk limit applies to DDR5/DDR6 designs?

A4: Crosstalk must be ≤–35dB. DDR6 requires the 5W spacing rule; DDR5 uses 3W. Guard traces are used in dense hdi pcb areas.

If you need professional high speed PCB impedance design support or quotation, our team provides free DFM check and fast turnaround.

![Understanding PCB Costs & Pricing [Your Complete Guide] Understanding PCB Costs & Pricing [Your Complete Guide]](https://hdicircuitboard.com/wp-content/uploads/elementor/thumbs/Understanding-PCB-Costs-Pricing-Your-Complete-Guide-qzzhe6mcaxuolkux3xalfktgavumi9y1aqfbs9bpv4.webp)