A. Real Pain Points for Engineers & Procurers

- Annular rings <2mil cause 35% of via breakout failures in high density interconnect pcb production.

- Unverified stackup compatibility with manufacturer capabilities adds 14–21 days to hdi printed circuit boards lead time.

- Trace spacing at minimum factory limits (2mil) reduces yield by 28% due to crosstalk and short circuits.

- Missing via fill specifications for via-in-pad leads to 40% of BGA solder wicking issues in hdi board assembly.

- Ignoring copper roughness (>1μm) for 50Gbps+ signals increases insertion loss by 0.2dB/inch @20GHz.

- Incomplete Gerber files result in 18% of hdi pcb redesigns, inflating costs by 60%.

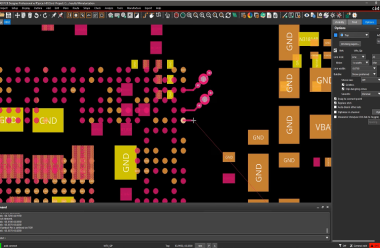

Learn more about : 2026 HDI PCB Design Guidelines

B. Core Technical Points

1. Material Selection Errors & Mitigation

Common Material Mistakes

- Using standard FR4 for 25Gbps+ signals (Df=0.01–0.02) instead of low-loss alternatives

- Impact: Insertion loss 0.5dB/inch @20GHz vs. 0.3dB/inch for Isola I-Speed

- CTE mismatch (>3ppm/°C) between core and buildup layers

- Risk: 27% microvia cracking after 1000 thermal cycles (-40°C to 125°C)

- Overlooking moisture absorption (>0.15%) for harsh environments

- Consequence: Delamination during lead-free reflow (260°C peak)

Material Selection Solutions

| Material | Dk @10GHz | Df @10GHz | Tg (°C) | Speed Range | HDI Application |

|---|---|---|---|---|---|

| FR408HR | 3.48–3.67 | 0.0093–0.0098 | 180 | 10–25Gbps | Enterprise switches |

| Isola I-Speed | 3.45–3.55 | 0.0059 | 180 | 25–50Gbps | 5G small cells |

| Rogers 4350B | 3.48 | 0.0017 | 180 | ≥25Gbps | RF/microwave modules |

| Astra MT77 | 2.95–3.01 | 0.0017–0.0019 | 200 | 60–100GHz | mmWave AiP |

- Quality Control: Verify Dk/Df via VNA at 1GHz/10GHz/20GHz per IPC-TM-650 2.5.5.12

Learn more about: Materials for HDI PCB: Full Classification Guide

2. Stackup & Layer Design Mistakes

Critical Stackup Errors

- Asymmetric layer configuration (e.g., Signal-GND-Signal-Power)

- Issue: Warpage >0.7mm/m for 16-layer high density interconnect pcb

- Insufficient reference planes (1 ground plane for 4 signal layers)

- Impact: Crosstalk >-30dB for 50Gbps signals (IPC-6012 Class 3 failure)

- Excessive dielectric thickness (>6mil) for signal layers

- Problem: Trace width ≥5mil (reduces routing density by 30%)

Proper Stackup Guidelines

- Symmetric stackup (e.g., Signal-GND-Power-GND-Signal) with uniform copper distribution (±10%)

- 1 ground/power plane per 2 signal layers to minimize loop area <100mm²

- Dielectric thickness: 2–4mil (signal layers), 8–12mil (core layers)

- Compliance: IPC-2226 for HDI stackup classification (Type I–VI)

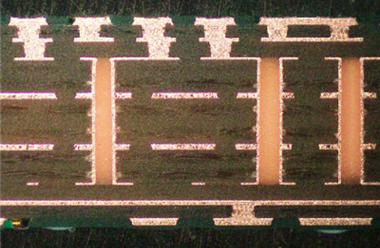

3. Microvia & Via Design Errors

Microvia Specification Mistakes

- Aspect ratio >0.75:1 (e.g., 5mil diameter, 5mil dielectric)

- Manufacturing Risk: 40% via plating voids (holes >50μm)

- Annular ring <2mil (0.05mm)

- Consequence: Via breakout and open circuits due to registration tolerance

- Unspecified via fill for via-in-pad

- Issue: Solder wicking during reflow, causing BGA tombstoning

Via Design Solutions

- Microvia parameters: 4–6mil diameter, aspect ratio ≤0.75:1 (IPC-6016)

- Annular ring minimum 2mil (0.05mm), 3mil for outer layers

- Via-in-pad: Copper-filled (≥98% fill density) + planarization ≤5μm (IPC-4761 Type VII)

- Quality Control: X-ray inspection for 100% of stacked microvias

4. Signal Integrity & Routing Mistakes

Routing Errors Impacting Performance

- 90° trace bends for high-speed signals

- Impact: 8% impedance deviation (54Ω vs. target 50Ω)

- Trace length mismatch >3mil for differential pairs

- Problem: Eye diagram closure for 100Gbps SerDes (BER >1e-12)

- Insufficient trace spacing (<2x trace width)

- Risk: Crosstalk >-30dB for adjacent high-speed traces

Signal Integrity Best Practices

- Trace dimensions by speed:

- ≤10Gbps: 4mil width, 3mil spacing

- 10–25Gbps: 3.5mil width, 3mil spacing

- ≥25Gbps: 3mil width, 2.5mil spacing

- Use 45° bends (radius ≥3x trace width) and differential pair routing

- Guard traces (3mil width, grounded) between sensitive signals

- Impedance tolerance: ±2% (100Gbps+), ±5% (≤25Gbps)

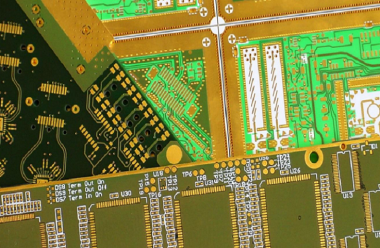

5. Manufacturing & DFM Errors

DFM Mistakes Leading to Yield Loss

- Trace/space below factory capability (≤2mil for low-volume production)

- Impact: Yield 72% vs. 95% for 2.5mil/2.5mil

- Inadequate solder mask dams (<3mil) between fine-pitch pads

- Consequence: Solder bridging (15% defect rate for 0.5mm BGA)

- Missing fabrication documentation (via types, impedance values)

- Risk: Manufacturer assumptions leading to functional failure

DFM Compliance Guidelines

- Confirm factory minimums: 2.5mil/2.5mil trace/space, 4mil microvia diameter

- Solder mask dams ≥3mil between pads; registration tolerance ±0.5mil

- Fabrication notes must include:

- Full stackup (materials, thicknesses, copper weights)

- Via types, sizes, and fill requirements

- Controlled impedance values and tolerances

- IPC class (Class 2/3) and surface finish (ENIG/ENEPIG)

6. Application-Specific Design Errors

Industry-Specific Mistakes

- Automotive ADAS: Tg <180°C for underhood hdi circuit boards

- Risk: Resin softening at 125°C (ISO 26262 non-compliance)

- 5G mmWave: Copper roughness >0.8μm

- Impact: 0.22dB/inch extra loss @60GHz

- AI Servers: Insufficient thermal vias (spacing >150mil)

- Problem: Hotspot temperature >130°C (component failure)

Application-Specific Fixes

- Automotive: Use High-Tg FR4 (Tg ≥180°C) or TU933+ (Tg 220°C)

- 5G mmWave: Rolled copper (Ra ≤0.8μm) or ULP copper (Ra ≤0.5μm)

- AI Servers: 6mil thermal vias (100mil spacing) under high-power ICs

- Medical Devices: Biocompatible solder mask + 100% visual inspection (IPC-6012 Class 3)

7. Early Manufacturer Collaboration

Collaboration Benefits

- Validate stackup feasibility before design finalization

- Avoids custom material orders (lead time +21 days)

- Get manufacturer-specific DFM rules

- Reduces redesign risk by 40%

- Review via structures and lamination capabilities

- Ensures compatibility with sequential lamination (up to 4 cycles)

Collaboration Checklist

- Share preliminary stackup and via design within 2 weeks of project start

- Request manufacturer’s stackup templates and DFM guidelines

- Conduct design reviews at 30%, 60%, and 90% completion stages

- Confirm laser drilling capabilities (power, speed, minimum diameter)

8. Gerber File Audit

Common Gerber Errors

- Missing drill files or layer assignments

- Incorrect solder mask specifications

- Lack of impedance and netlist information

- Unlabeled reference planes and power layers

Gerber Audit Checklist

- Include all layers (signal, power, ground, solder mask, silkscreen)

- Verify drill file accuracy (diameters, locations, plating specs)

- Add netlist and impedance reports

- Label all layers and include version control

- Use Gerber X2 format for enhanced manufacturability

9. Key Comparisons for Error Prevention

Stacked vs. Staggered Microvias

| Aspect | Stacked Microvias | Staggered Microvias |

|---|---|---|

| Density | Higher (saves 30% space) | Lower |

| Reliability | 20% more prone to thermal failure | More robust (40% fewer cracks) |

| Cost | 30% premium | Cost-effective |

| Best For | AI/HPC (high density) | Automotive/industrial (reliability) |

Learn more about: How to Choose Between Microvias, Stacked Vias, and Staggered Vias for High Density Interconnect (HDI) PCBs

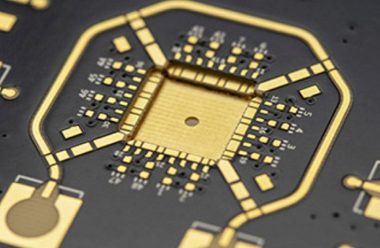

ENIG vs. ENEPIG Surface Finishes

| Aspect | ENIG | ENEPIG |

|---|---|---|

| Solderability | Good | Excellent (better for fine-pitch BGA) |

| Corrosion Resistance | High | Higher |

| Cost | 1x | 1.5x |

| Best For | General HDI | Medical/automotive (high reliability) |

C. Real Factory Case Study

12-Layer HDI for 50Gbps Data Center Switch

Project Specifications

- Stackup: 2+8+2 buildup (12-layer high density interconnect pcb)

- Materials: Isola I-Speed (signal layers), High-Tg FR4 (core)

- Parameters: 50Ω/100Ω impedance, 3mil/3mil trace/space, 5mil stacked microvias

- Application: 50Gbps Ethernet switch (data center)

Issues Encountered

- Annular ring <2mil caused 22% via breakout during drilling

- Missing via fill specs for via-in-pad led to 35% BGA solder wicking

- Asymmetric stackup resulted in 0.8mm/m warpage (component placement failure)

- Trace spacing 2mil caused crosstalk >-28dB (signal integrity test failure)

Implemented Fixes

- Increased annular ring to 3mil (outer layers) and 2.5mil (inner layers)

- Specified copper-filled via-in-pad (98% fill density) + planarization ≤5μm

- Restacked layers to symmetric Signal-GND-Power-GND-Signal configuration

- Adjusted trace spacing to 3mil (25Gbps+ signals)

- Collaborated with manufacturer to validate DFM rules pre-production

Results

- Yield increased from 72% to 94%

- Warpage reduced to 0.3mm/m (within assembly limits)

- Crosstalk improved to -35dB (meets IPC-6012 Class 3)

- Solder wicking defects eliminated (0% BGA failures)

- Production lead time reduced by 12 days

D. Common Design Errors (Production Perspective)

- Using through-hole vias in high-density areas: Blocks 3x more routing space than microvias.

- Neglecting decoupling capacitor placement (>50mil from IC power pins): Increases voltage noise by 200mV.

- Splitting ground planes: Creates ground loops and increases EMI by 18dB.

- Overlooking trace necking (width <2mil between pads): Causes current density issues (1.5x higher temperature).

- Using 0.3mm drill diameter for standard vias: Reduces current capacity by 30% vs. 0.4mm.

- Missing thermal relief pads for power components: Impairs heat dissipation (hotspot temp +40°C).

E. FAQ

- What is the difference between PCB and PCA in terms of design errors? PCB design errors relate to board structure (traces, vias, stackup), while PCA errors involve component assembly (soldering, placement). HDI PCB errors like microvia aspect ratio violations often lead to PCA failures such as BGA solder defects.

- How to avoid via-in-pad solder wicking in HDI PCB? Specify copper-filled or non-conductive filled vias with planarization ≤5μm (IPC-4761 Type VII) and solder mask coverage over the via. Avoid unfilled vias in SMD pads, especially for fine-pitch BGAs (≤0.5mm pitch).

- Which surface finish is best for fine-pitch HDI PCB? ENEPIG (Electroless Nickel Electroless Palladium Immersion Gold) is ideal for fine-pitch BGAs (≤0.5mm) due to superior solderability and corrosion resistance. ENIG is a cost-effective alternative for pitches ≥0.8mm.

- How to ensure Gerber files are error-free for HDI PCB production? Include all layers (signal, power, ground, solder mask, silkscreen), drill files with plating specs, impedance reports, netlist, and fabrication notes. Use Gerber X2 format and conduct a manufacturer pre-production review to catch missing or incorrect data.

If you need professional HDI PCB design support or quotation, our team provides free DFM check and fast turnaround.

![Understanding PCB Costs & Pricing [Your Complete Guide] Understanding PCB Costs & Pricing [Your Complete Guide]](https://hdicircuitboard.com/wp-content/uploads/elementor/thumbs/Understanding-PCB-Costs-Pricing-Your-Complete-Guide-qzzhe6mcaxuolkux3xalfktgavumi9y1aqfbs9bpv4.webp)