How to Choose HDI Stackup for Your Project: Complete Guide

Electronic engineers designing high density interconnect PCBs and procurement teams sourcing them face persistent challenges balancing routing density, signal integrity, and manufacturing feasibility. Many struggle to select the right HDI stackup structure—from 1+N+1 to 4+N+4—for their specific application requirements, while procurement teams often grapple with cost variations, lead time differences, and supplier capability gaps across stackup types. Choosing the wrong HDI stackup leads to costly reworks, signal degradation, or over-engineered solutions that drive up production costs. This guide breaks down the systematic process of selecting an HDI stackup from a factory engineer’s perspective, with actionable parameters, real production insights, and clear decision frameworks to master high density interconnect PCB stackup selection.

Learn more about : 50Ω / 75Ω / 100Ω Impedance in High Density Interconnect (HDI) PCBs: Design & Production Guide

Pre-Design Preparation & Requirement Alignment

Define Core Design Requirements First

Start with quantifiable design parameters to narrow stackup options, ensuring alignment with functional needs:

- Signal Speed Targets: ≤10Gbps (basic HDI), 10–50Gbps (moderate), 50–100Gbps (advanced)

- Routing Density Needs: 60–80 pins/sq.in. (low), 80–120 pins/sq.in. (moderate), ≥120 pins/sq.in. (high)

- Component Pitch: ≥0.8mm (coarse), 0.5–0.65mm (fine), ≤0.5mm (ultra-fine)

- Impedance Requirements: 50Ω (single-ended, ±3–10%), 90/100Ω (differential, ±3–10%)

- Mechanical Constraints: Board thickness (0.4–3.0mm), form factor (compact/standard), weight limits

- Environmental Specifications: Operating temperature (-40°C to +125°C), humidity resistance (85% RH)

Review IPC Standards Compliance

HDI stackup selection must adhere to industry standards to ensure manufacturability and reliability:

- IPC-2221: Governs trace/space, via, and stackup design rules (minimum 20μm line/space for HDI)

- IPC-6016: Defines HDI-specific performance and reliability criteria (microvia aspect ratio ≤0.8:1)

- IPC-4104: Specifies dielectric material qualifications for high-density structures

- IPC-2226: Classifies HDI types (I–VI) based on core and microvia layer arrangements

Core Stackup Architecture Design

Evaluate HDI Stackup Structure Options

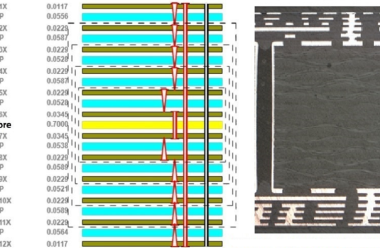

Compare the four primary HDI stackup architectures to match design complexity and performance needs:

| HDI Stackup Type | Total Layers (Typical) | Build-Up Layers (Per Side) | Core Layers (N) | Key Specs | Ideal Applications |

|---|---|---|---|---|---|

| 1+N+1 | 4–10 | 1 | 2–8 | 25–50μm line/space, 50–100μm microvias | Wearables, basic sensors, cost-sensitive consumer electronics |

| 2+N+2 | 8–16 | 2 | 4–12 | 20–40μm line/space, stacked/staggered microvias | 5G modules, smartphones, automotive ADAS, high-speed routers |

| 3+N+3 | 14–22 | 3 | 8–16 | 15–35μm line/space, copper-filled vias | AI accelerators, HPC, aerospace electronics, complex SoCs |

| 4+N+4 | 18–28 | 4 | 10–20 | 12–30μm line/space, ultra-fine microvias | 100Gbps+ systems, satellite communication, military electronics |

Learn more about :How Does High Density Interconnect (HDI) Affect BGA Fanout and Component Placement?

Plane Pair Configuration

Optimize power and ground plane placement to enhance signal integrity and reduce noise:

- Plane Pairing: 1 power plane + 1 ground plane per 2–3 signal layers (lowers PDN impedance)

- Plane Continuity: No splits under impedance-controlled traces; use stitching vias (1mm spacing) if splits are unavoidable

- Anti-Pad Sizing: 1.5x microvia diameter to prevent short circuits between vias and planes

- Symmetry Requirement: Maintain symmetric layer arrangement to avoid warpage (≤0.5% per IPC limits)

Material Selection for Performance & Manufacturability

Dielectric Material Options

Choose dielectric materials based on stackup complexity and electrical performance needs:

| Material Type | Dk (10GHz) | Df (10GHz) | Tg (°C) | Stackup Suitability | Key Benefit |

|---|---|---|---|---|---|

| Standard FR-4 | 4.2–4.6 | 0.015–0.020 | 130–140 | 1+N+1 | Low cost, widely available |

| High-Tg FR-4 | 4.0–4.3 | 0.012–0.015 | 170–180 | 1+N+1/2+N+2 | Thermal stability, cost-effective |

| Low-Loss FR-4 | 3.8–4.0 | 0.008–0.010 | 160–170 | 2+N+2/3+N+3 | Balanced performance, moderate cost |

| Ceramic-Filled | 3.0–3.5 | 0.003–0.005 | 180–200 | 3+N+3/4+N+4 | Low loss, high stability |

| PTFE-Based | 2.1–2.3 | 0.001–0.002 | 260+ | 4+N+4 (RF) | Ultra-low loss, high-frequency performance |

Copper Specifications

Select copper properties to balance current capacity and signal integrity:

- Thickness: 0.5oz (18μm) for build-up layers (optimal for microvia plating), 0.5–2oz (18–70μm) for core layers

- Type: Electrodeposited (ED) copper (standard, cost-effective) or rolled copper (low roughness, ideal for high-speed designs)

- Surface Roughness: ≤1μm for high-frequency applications (reduces conductor loss)

Via Structure Integration & Optimization

Microvia Design Considerations

Microvia parameters directly impact stackup performance and manufacturability:

- Diameter: 50–100μm (1+N+1/2+N+2), 40–80μm (3+N+3/4+N+4)

- Aspect Ratio: ≤0.8:1 (depth/diameter) per IPC-6016 for reliable plating

- Arrangement: Staggered (cost-effective) or stacked (high-density); max 3 stacked layers

- Fill Type: Non-conductive epoxy (1+N+1/2+N+2) or copper fill (3+N+3/4+N+4 for thermal conductivity)

Blind/Buried Via Implementation

Incorporate blind and buried vias to maximize routing density and reduce signal path length:

- Blind Vias: Connect outer build-up layers to core (100–150μm diameter); no full-board penetration

- Buried Vias: Connect inner core layers (100–200μm diameter); no surface exposure

- Via-in-Pad: Filled/capped for fine-pitch BGAs (0.3–0.5mm pitch); pad diameter 2x microvia diameter

- Skip Vias: Route from surface layer to deeper core layers (e.g., L1→L3) to avoid stacked microvias

Manufacturing Process Alignment

Lamination & Drilling Requirements

Align stackup selection with manufacturing process capabilities:

- Lamination Cycles: 1 (1+N+1), 2 (2+N+2), 3–4 (3+N+3/4+N+4); each cycle adds 3–5 days to lead time

- Pressure/Temperature Control: 40–75psi, 170–180°C for FR-4; adjusted for specialty materials

- Drilling Technology: UV laser for microvias (±5μm positioning accuracy), mechanical drilling for core vias (≥150μm diameter)

- Registration Tolerance: ±2μm for build-up layers, ±3μm for core layers (critical for stacked vias)

Quality Control & Testing Protocols

Define quality checks to ensure stackup integrity and performance:

- In-Process Testing: Trace width (±2μm), dielectric thickness (±3μm), via plating thickness (15–20μm)

- Final Validation: TDR impedance testing (±3–10% tolerance), AOI inspection, cross-section analysis (5% of production)

- Environmental Stress Testing: Thermal cycling (-40°C to +125°C, 100 cycles) for high-reliability applications

- X-Ray Inspection: 3D X-ray for microvia plating quality and stacked via alignment (3+N+3/4+N+4)

Consider Material & Manufacturing Factors

Cost & Lead Time Tradeoffs

Balance technical requirements with practical commercial constraints:

- Cost Breakdown: Per-unit cost increases by 30–40% per additional build-up layer set (i)

- Lead Time Estimates: 5–10 days (1+N+1), 7–14 days (2+N+2), 10–18 days (3+N+3), 14–25 days (4+N+4)

- NRE Costs: Higher for complex stackups (3+N+3/4+N+4) due to specialized tooling and setup

- Volume Impact: Low volume (<1k units) favors simpler stackups (1+N+1/2+N+2) to avoid excessive NRE

Supplier Capability Assessment

Verify manufacturer capabilities to ensure stackup feasibility:

- Equipment Readiness: Laser drilling (≤40μm diameter), sequential lamination, and copper filling capacity

- Process Certifications: Compliance with IPC standards, ISO 9001, and industry-specific qualifications (aerospace/medical)

- Material Sourcing: Access to specialty laminates (PTFE, ceramic-filled) for advanced stackups

- Yield History: Minimum 90% yield for complex stackups (3+N+3/4+N+4)

Validate with IPC Standards & DFM Rules

Design for Manufacturability (DFM) Checks

Ensure stackup design aligns with manufacturing capabilities to avoid reworks:

- Trace/Space Verification: Minimum 20μm line/space for HDI (per IPC-2221)

- Microvia Aspect Ratio: ≤0.8:1 to prevent plating defects

- Dielectric Thickness: 10–30μm for build-up layers (±3μm tolerance)

- Symmetry Check: Mirror layer arrangement to prevent warpage

- Tooling Considerations: Include test coupons for impedance and quality verification

Simulation & Prototyping Validation

Validate stackup performance before full-scale production:

- Signal Integrity Simulation: Test crosstalk (≤-35dB at 25Gbps), insertion loss (≤0.5dB/in at 25Gbps)

- Power Integrity Analysis: Ensure PDN impedance meets target (≤20mΩ at 1GHz)

- Prototype Testing: Produce small-batch prototypes (5–10 units) to verify stackup performance

- Design Iteration: Adjust stackup based on prototype results (e.g., material changes for signal integrity)

Factory HDI Stackup Selection Case Study

Project Overview & Initial Parameters

A 5G infrastructure equipment manufacturer needed an HDI stackup for a 40Gbps base station module, with conflicting goals of high performance and cost efficiency:

- Key Requirements: 0.5mm pitch BGA (484 pins), 40Gbps signal support, 12-layer count, 1.6mm thickness

- Initial Stackup Choice: 1+10+1 (12-layer) – selected for cost savings

- Critical Specs: 50Ω single-ended (±5%), 100Ω differential (±5%); 25μm line/space; ENIG surface finish

Selection Challenges & Root Causes

The initial 1+10+1 stackup failed to meet performance targets during feasibility testing:

- Signal Integrity Gaps: 40Gbps signals suffered -20dB crosstalk (target: ≤-30dB) – root cause: insufficient build-up layers for proper grounding

- Microvia Plating Issues: 100μm microvias had 12–15μm plating thickness (target: 18μm) – root cause: aspect ratio exceeded 1:1 in 1+10+1 structure

- Routing Congestion: Could not route 484-pin BGA with 25μm line/space – root cause: limited build-up layers restricted fanout capability

Revised Stackup Selection & Quantified Results

The factory recommended switching to a 2+8+2 (12-layer) stackup, with targeted adjustments:

- Stackup Redesign: 2 build-up layers per side (15μm dielectric each) – enabled staggered microvias and additional ground plane

- Microvia Optimization: Reduced microvia diameter to 80μm (aspect ratio 0.8:1) – achieved 18–20μm plating thickness

- Material Upgrade: Selected low-loss FR-4 (Dk 3.8, Df 0.008) for build-up layers – improved signal integrity

Final Results: 94% production yield, 40Gbps signal crosstalk ≤-35dB, impedance variation ±4% (meets target). Per-unit cost increased by 18% vs. 1+10+1, but total project cost decreased by 22% due to reduced rework and improved performance. The 2+8+2 stackup enabled the base station module to meet latency requirements (≤10ns) and pass environmental stress testing.

Common Design Errors (Production End Perspective)

H3: Stackup Selection Mistakes

From a factory engineer perspective, 70% of HDI stackup-related failures stem from incorrect structure selection:

- Over-Engineering: Specifying 3+N+3 for 10Gbps signals (1+N+1 sufficient) – increases cost by 40–60% (40% of errors)

- Under-Engineering: Using 1+N+1 for ≤0.5mm pitch BGAs – causes routing congestion and signal degradation (20% of errors)

- Ignoring Symmetry: Designing asymmetric 2+N+2 stackups – leads to warpage (≥0.8%) and assembly issues (15% of errors)

- Mismatched Via/Stackup: Using stacked vias in 1+N+1 – creates plating voids and reliability risks (10% of errors)

- Incorrect Core Layer Count: Selecting N=4 for 2+N+2 (8-layer) when N=6 is needed – reduces routing density (15% of errors)

Material & Process Mismatches

Avoid these common errors that compromise stackup performance:

- Using Standard FR-4 for High-Speed Designs: Causes signal loss ≥30% at 25Gbps – use low-loss materials for 2+N+2 and above

- Inadequate Plane Pairing: <1 ground plane per 3 signal layers – increases crosstalk by 10–15dB

- Excessive Stacked Vias: >3 stacked microvias – causes lamination delamination in reflow

- Ignoring Manufacturing Tolerances: Designing for exact dielectric thickness (no ±3μm buffer) – leads to impedance drift

- Incorrect Anti-Pad Sizing: <1.5x microvia diameter – causes short circuits between vias and planes

FAQ – How to Choose HDI Stackup for Your Project

1. When should I choose 2+N+2 over 1+N+1 for HDI PCBs?

Choose 2+N+2 over 1+N+1 when your high density interconnect PCB requires 0.5–0.65mm pitch BGAs, 10–50Gbps signal speeds, or 80–120 pins/sq.in. routing density. 2+N+2 is also preferred for designs needing stacked microvias or improved signal integrity (crosstalk ≤-35dB) – common in smartphones, 5G modules, and automotive ADAS. 1+N+1 remains viable for cost-sensitive, low-speed (≤10Gbps) applications with ≥0.8mm pitch components.

2. What material is best for HDI stackups in high-temperature environments?

For operating temperatures above 125°C, ceramic-filled laminates (Dk 3.0–3.5, Tg 180–200°C) are ideal – they maintain structural stability and electrical performance in extreme heat. High-Tg FR-4 (Tg ≥170°C) is a cost-effective alternative for temperatures up to 125°C. Avoid standard FR-4 (Tg 130–140°C) for high-temperature applications, as it can soften and degrade during reflow or operation.

3. How does HDI stackup affect manufacturing lead time and cost?

Each additional set of build-up layers (i) increases HDI PCB manufacturing lead time by 3–5 days and cost by 30–40%. For example:

- 1+8+1 (10-layer): 7–10 days lead time, $15–20 per unit (1k volume)

- 2+8+2 (12-layer): 10–14 days lead time, $22–28 per unit (1k volume)

- 3+8+3 (14-layer): 14–18 days lead time, $35–45 per unit (1k volume)Cost drivers include additional lamination cycles, precision alignment, and advanced testing (3D X-ray, impedance mapping) required for complex stackups.

4. Can I mix build-up layer counts (e.g., 2+N+3) for HDI PCBs?

Mixing build-up layer counts (asymmetric i values) is not recommended for high density interconnect PCBs. Asymmetric stackups (e.g., 2+8+3) create uneven thermal expansion and lamination stress, leading to warpage (≥1.0% vs. ≤0.5% for symmetric) and reduced reliability. Additionally, asymmetric designs complicate impedance control (variation ±2–3% higher) and increase manufacturing complexity (custom tooling, longer setup time). IPC-2226 mandates symmetric build-up layers for HDI PCBs to ensure structural and electrical stability.