High speed PCB design in 2026 demands precision alignment of signal integrity, material science, and manufacturing capabilities—especially for hdi pcb and low loss applications. This guide integrates IPC standards, real-world production parameters, and HDI PCB best practices to deliver reliable, high-performance boards that meet multi-gigabit data rate requirements while minimizing crosstalk, reflections, and EMI.

Learn more about: How To Route HDI PCB

Technical Points

1. What is High Speed PCB

Definition & Thresholds

- High-speed PCBs handle signals with edge rates <1ns (equating to >500MHz bandwidth) or data rates ≥1Gbps

- Critical length threshold: Trace length ≥ λ/12 (λ = signal wavelength in dielectric)

- Key indicators: Signal delay >20% of rise time, or interconnection length ≥ λm/12

- Encompasses high speed pcb, hdi pcb, Low Loss PCB, and ultra low loss pcb variants for specialized applications

Industry Standards & Classifications

- IPC-6012 Class 3 for high-reliability high speed pcb (aerospace, medical)

- IPC-2221 for trace width, spacing, and impedance calculations

- Differentiates by material loss: Low Loss PCB (Df ≤0.005), ultra low loss pcb (Df ≤0.002)

- HDI integration: Microvias (≤0.15mm) and sequential lamination for high-density high speed pcb

2. High-Speed PCB Design Guidelines

Foundational Design Rules

- Maintain controlled impedance: 50Ω (single-ended), 90–100Ω (differential pairs)

- Trace length matching: ±1mil for differential pairs, ±5% for parallel buses

- Reference plane continuity: No splits under high-speed traces (loop area <100mm²)

- Layer stack symmetry to limit warpage <0.4mm/m (IPC-6012 Class 2/3)

HDI-Specific Guidelines

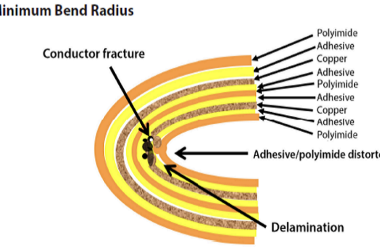

- Microvia aspect ratio ≤0.75:1 (drill diameter ≤0.15mm, depth ≤0.11mm)

- Staggered microvias preferred over stacked for thermal reliability (40% fewer cracks)

- Trace/space: 2.5mil/2.5mil (outer layers), 2mil/2mil (inner layers) for hdi circuit boards

- Via-in-pad: Copper-filled (≥98% fill density) + planarization ≤5μm

3. Signal Integrity

Key Performance Metrics

- Insertion loss: ≤0.3dB/inch @20GHz for Low Loss PCB; ≤0.15dB/inch @20GHz for ultra low loss pcb

- Return loss: ≥-15dB up to 25Gbps; ≥-20dB for 50Gbps+ signals

- Crosstalk: ≤-35dB between adjacent traces (IPC-2221)

- Jitter: ≤10% of bit period (e.g., ≤20ps for 50Gbps signals)

Mitigation Techniques

- Termination: Series resistors (47–50Ω) for source termination; parallel resistors for load termination

- Stub reduction: Backdrill through-hole vias to eliminate stubs >5mil

- Impedance control: Trace width 3–5mil (50Ω microstrip on 4mil dielectric)

- Reference plane stitching: Vias spaced λ/20 (e.g., 3mm @25GHz) to maintain return path

Learn more about : Signal Integrity in HDI PCB Design

4. Ground Planes

Design & Placement

- Dedicated ground plane for each high-speed signal layer (adjacent layer)

- Solid plane with no voids (breaks create impedance discontinuities >10Ω)

- Separate analog/digital ground planes tied at single point (star grounding)

- Ground pour on outer layers connected via stitching vias (100mil spacing)

HDI Ground Plane Considerations

- Ground plane clearance: 15mil from board edge; 10mil from v-score lines

- Antipad size: 16mil larger than microvia diameter (0.15mm via → 0.51mm antipad)

- Thermal relief pads for power components (4 spokes, 3mil width)

- Compliance: IPC-6012 Class 3 requires ground plane continuity ≥95%

5. Routing & Geometry

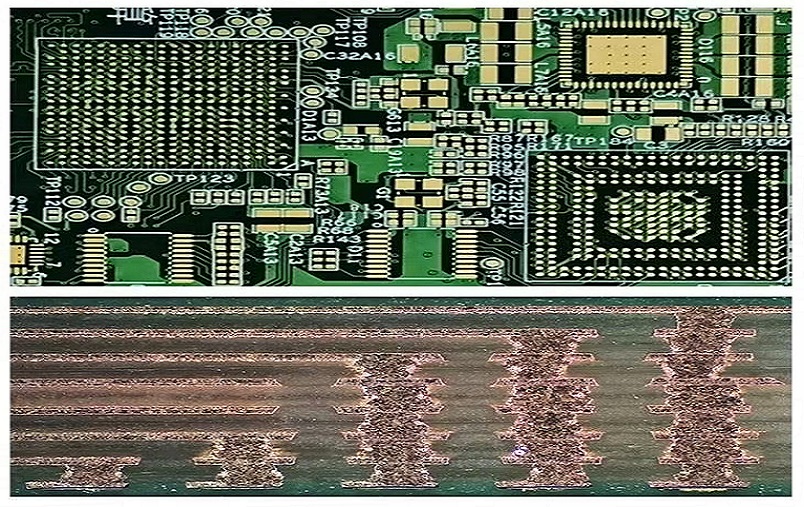

Trace Routing Rules

- Trace width: 3mil (≤25Gbps), 4mil (10–25Gbps), 5mil (≤10Gbps) for 1oz copper

- Bends: 45° angles (radius ≥3x trace width); avoid 90° bends for >10Gbps

- Differential pair routing: Parallel paths, constant spacing (3–5mil), length matching ±1mil

- Layer transitions: Minimize (≤2 vias per signal); symmetric vias for differential pairs

3W Rule Implementation

- Trace spacing ≥3x trace width (e.g., 3mil trace → 9mil spacing)

- Reduces crosstalk by 20–25dB in high-speed designs

- Exceptions: Dense HDI areas (minimum 2x width, crosstalk ≤-30dB)

- Validated for frequencies up to 100GHz (IPC-2221)

6. Crosstalk Reduction

Physical Separation & Shielding

- Guard traces: 3mil width, grounded, placed between sensitive signals

- Layer separation: Orthogonal routing on adjacent layers (reduces broadside crosstalk)

- Shielding cans for RF/high-speed sections (grounded to plane via 4 vias)

- Trace length parallelism: ≤100mil (beyond this, crosstalk increases exponentially)

Material & Impedance Tuning

- Low Dk materials (3.0–3.5) reduce field coupling between traces

- Impedance mismatch: Maintain ±5% tolerance (50Ω → 47.5–52.5Ω)

- AC coupling capacitors: Placed symmetrically (0402 package) within 50mil of TX/RX pins

- Simulation: 3D field solver verification for crosstalk < -35dB

Learn more about : HDI PCB Impedance Control: Design, Manufacturing & Performance Guide

7. Via Usage

Via Specifications

- Through-hole vias: 0.3–0.4mm diameter, aspect ratio ≤10:1

- Microvias: 0.1–0.15mm diameter, laser-drilled (aspect ratio ≤0.75:1)

- Blind/buried vias: Connect 2–3 layers (no full penetration)

- Stitching vias: 0.2mm diameter, 100mil spacing, grounded to reference planes

HDI Via Best Practices

- Multiple return vias (4 per signal via) to reduce inductance <1nH

- Via-in-pad: No solder mask (opens for BGA pads); filled with copper

- Backdrilling: Remove stubs >5mil for 25Gbps+ signals

- Quality control: X-ray inspection for via fill density ≥98% (IPC-6016)

8. Material Selection

Low Loss & Ultra Low Loss Options

| Material | Dk @10GHz | Df @10GHz | Tg (°C) | Application |

|---|---|---|---|---|

| FR408HR | 3.48–3.67 | 0.0093–0.0098 | 180 | General high speed pcb |

| Isola I-Speed | 3.45–3.55 | 0.0059 | 180 | Low Loss PCB (≤50Gbps) |

| Rogers 4350B | 3.48 | 0.0017 | 180 | ultra low loss pcb (≥50Gbps) |

| Astra MT77 | 2.95–3.01 | 0.0017–0.0019 | 200 | 60–100GHz high speed pcb |

Material Compatibility

- CTE matching: Core/buildup layers ≤3ppm/°C difference (reduces microvia cracking)

- Moisture absorption: ≤0.15% (prevents delamination during reflow)

- Copper weight: 1–2oz (balances current capacity and impedance control)

- Dielectric thickness: 4mil (signal layers), 8–12mil (core layers)

9. Material and Stackup

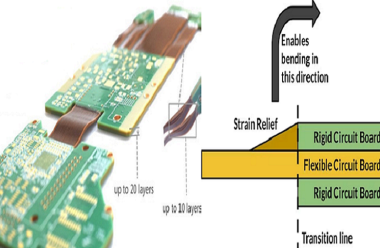

Stackup Design

- Symmetric structure (e.g., Signal-GND-Power-GND-Signal) for 4-layer boards

- HDI stackup: 2+N+2 (2 buildup layers, N core layers)

- Dielectric thickness tolerance: ±10% (critical for impedance control)

- Copper distribution: Uniform (±10%) across layers to prevent warpage

Early Fabrication Involvement

- Validate stackup with manufacturer within 2 weeks of design start

- Confirm laser drilling capabilities (minimum 0.1mm diameter)

- Review lamination cycles (max 4 for sequential HDI)

- Pre-production test coupons for impedance verification (50Ω/100Ω)

10. Surface Finish and Testing

Finishes for High-Speed Performance

- ENIG: Ni 3–6μm, Au 0.05–0.15μm (general high speed pcb)

- ENEPIG: Ni 3–6μm, Pd 0.1–0.2μm, Au 0.05μm (fine-pitch HDI)

- Immersion Silver: 0.8–1.2μm (cost-effective Low Loss PCB)

- Compliance: IPC-4552 (ENIG), IPC-4556 (ENEPIG)

Testing Requirements

- Impedance testing: TDR (Time Domain Reflectometry) ±2% tolerance

- Signal integrity: Eye diagram analysis (BER ≤1e-12 for 50Gbps)

- Thermal cycling: -40°C to 125°C, 1000 cycles (no microvia cracking)

- X-ray inspection: 100% via fill and annular ring verification

11. Fabrication Guidelines

Annular Rings

- Outer layers: ≥2mil (Class 2), ≥3mil (Class 3)

- Inner layers: ≥1.5mil (Class 2), ≥2mil (Class 3)

- Minimum lateral spacing: 1mil (Class 3) to prevent breakout

- Calculation: Annular ring = (Pad diameter – Drill diameter)/2

Board Edge & Data Package

- Board edge clearance: 15mil (traces), 20mil (vias)

- Panelization: V-score or mouse bites (10mil from copper features)

- Data package: Gerber X2 files + netlist + stackup diagram + impedance report

- Fabrication notes: Include IPC class, surface finish, and microvia specifications

12. Key Comparison Tables

Low Loss vs. Ultra Low Loss Materials

| Aspect | Low Loss PCB | Ultra Low Loss PCB |

|---|---|---|

| Df @10GHz | 0.003–0.006 | ≤0.002 |

| Speed Range | 25–50Gbps | ≥50Gbps |

| Cost | 1.5x FR4 | 3–4x FR4 |

| Best For | 5G, PCIe 5.0 | 112G SerDes, mmWave |

Through-Hole vs. Microvias in High-Speed Design

| Aspect | Through-Hole Vias | Microvias |

|---|---|---|

| Inductance | 1.5–2nH | 0.3–0.5nH |

| Density | Low (blocks routing) | High (saves 30% space) |

| Signal Speed | ≤10Gbps | ≥25Gbps |

| Manufacturing Cost | Low | 2x higher |

Factory Case Study

8-Layer HDI High Speed PCB for 50Gbps Data Center Switch

Project Specifications

- Stackup: 2+4+2 HDI structure (8-layer high speed pcb)

- Materials: Isola I-Speed (Low Loss PCB), Tg 180°C, Dk 3.45, Df 0.0059

- Parameters: 50Ω single-ended, 100Ω differential; 3mil/3mil trace/space; 0.12mm microvias

- Application: 50Gbps Ethernet switch (data center)

Issues Encountered

- Annular ring 1.5mil (outer layers) caused 28% via breakout during drilling

- Unstitched ground planes led to crosstalk >-28dB (IPC Class 3 failure)

- Via stubs >8mil resulted in return loss < -12dB @50GHz

- Material mismatch (CTE difference 5ppm/°C) caused microvia cracking after thermal cycling

Improvements Implemented

- Increased annular ring to 3mil (outer layers) and 2mil (inner layers)

- Added stitching vias (0.2mm diameter, 100mil spacing) to ground planes

- Backdrilled through-hole vias to eliminate stubs >5mil

- Selected matching core/buildup materials (CTE difference ≤2ppm/°C)

- Collaborated with manufacturer for pre-production DFM review

Results

- Yield improved from 70% to 95%

- Crosstalk reduced to -38dB (meets IPC Class 3)

- Return loss ≥-18dB @50GHz

- Thermal cycle failure rate (1000 cycles) reduced from 15% to 1%

- Production lead time shortened by 10 days

Common Design Errors

- Using FR4 for >25Gbps signals (Df too high, insertion loss >0.5dB/inch @20GHz)

- Ignoring 3W rule (trace spacing <2x width) leading to crosstalk failures

- Split ground planes creating loop areas >200mm² (EMI >40dBμV/m)

- Microvia aspect ratio >0.75:1 (0.15mm diameter, 0.12mm depth → 0.8:1) causing plating voids

- Inadequate annular rings (<1.5mil) resulting in via breakout and open circuits

- Missing backdrilling for stubs >5mil (25Gbps+ signals suffer reflections)

- Using leaded components (ESL >2nH) in high-speed signal paths

- Incorrect stackup symmetry leading to warpage >0.8mm/m (assembly issues)

FAQ

1. When should I use ultra low loss pcb instead of Low Loss PCB?

Ultra low loss pcb (Df ≤0.002) is required for data rates ≥50Gbps, mmWave applications (60–100GHz), or trace lengths >6 inches. Low Loss PCB (Df 0.003–0.006) is cost-effective for 25–50Gbps signals or shorter trace lengths (<6 inches), balancing performance and manufacturing costs.

2. How to ensure via reliability in high-speed HDI PCB?

Use microvias with diameter 0.1–0.15mm and aspect ratio ≤0.75:1, implement multiple return vias (4 per signal via) to reduce inductance, specify copper-filled via-in-pad for BGA areas, and validate via fill density ≥98% via X-ray inspection. Avoid stacked microvias for high-temperature applications (use staggered instead).

3. What are the key fabrication requirements for high speed pcb?

Fabrication must meet IPC-6012 Class 3 for high-reliability applications, include controlled impedance testing (±2% tolerance), use laser drilling for microvias, maintain dielectric thickness tolerance ±10%, and provide test coupons for signal integrity verification. Early collaboration with the manufacturer ensures stackup and material compatibility.

If you need high speed PCB manufacturing or design support,our engineering team provides free DFM analysis and quotation.

![Understanding PCB Costs & Pricing [Your Complete Guide] Understanding PCB Costs & Pricing [Your Complete Guide]](https://hdicircuitboard.com/wp-content/uploads/elementor/thumbs/Understanding-PCB-Costs-Pricing-Your-Complete-Guide-qzzhe6mcaxuolkux3xalfktgavumi9y1aqfbs9bpv4.webp)