High-speed PCB refers to printed circuit boards optimized for signals with fast edge rates (≤1ns) or data rates ≥1Gbps, where physical characteristics of traces, materials, and layout directly impact signal integrity. This guide breaks down core definitions, technical requirements, and practical manufacturing insights to align high speed pcb, hdi pcb, Low Loss PCB, and ultra low loss pcb designs with industry standards and real-world production capabilities.

Learn more about : High-Speed PCB Design: The Ultimate Guide for 2026

Technical Points

1. What is High Speed Digital PCB

Definition & Core Principles

- High speed digital PCB handles signals where trace length ≥ λ/12 (λ = signal wavelength in dielectric) or signal delay >20% of rise time

- Distinguished by transmission line behavior, requiring controlled impedance and return path management

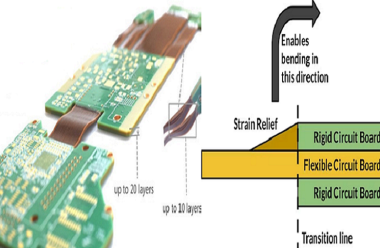

- Encompasses hdi pcb (high density interconnect) for compact designs and Low Loss/ultra low loss pcb for high-frequency applications

- Complies with IPC-6012 Class 2/3 and IPC-2221 standards for trace geometry and impedance control

Key Differentiators from Standard PCB

- Signal handling: ≥50MHz clock frequencies or ≥1Gbps data rates (e.g., PCIe 5.0, 10G Ethernet)

- Material requirements: Low Df (≤0.006 for Low Loss PCB; ≤0.002 for ultra low loss pcb)

- Layout constraints: Trace/space ≤3mil/3mil, impedance tolerance ±5%

- Manufacturing complexity: Supports microvias (≤0.15mm) and sequential lamination (hdi pcb)

2. Characteristics and Considerations

Electrical Performance Traits

- Controlled impedance: 50Ω (single-ended), 90–100Ω (differential pairs) per IPC-2221

- Insertion loss: ≤0.3dB/inch @20GHz (Low Loss PCB); ≤0.15dB/inch @20GHz (ultra low loss pcb)

- Crosstalk: ≤-35dB between adjacent traces (3W rule compliance)

- Propagation delay: ≤6ns/m (FR4); ≤5ns/m (ultra low loss materials)

Physical Design Considerations

- Layer count: 4–32 layers (hdi pcb up to 52 layers for advanced applications)

- Trace width: 3–5mil (50Ω microstrip on 4mil dielectric)

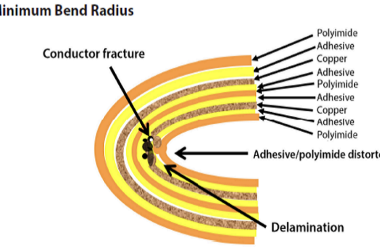

- Via specifications: Microvias (0.1–0.15mm), aspect ratio ≤0.75:1

- Stackup symmetry: Balanced copper distribution to limit warpage <0.4mm/m

3. Signaling Threshold

Speed and Frequency Benchmarks

- High-speed threshold: Rise time <1ns (equates to >500MHz bandwidth)

- Critical length: 2 inches (FR4) for 1ns rise time signals (λ/12 rule)

- Data rate correlations: 1Gbps = ~500MHz bandwidth; 10Gbps = ~5GHz bandwidth

- Clock frequency vs. edge rate: 100MHz clock with 1ns rise time = 500MHz effective bandwidth

Threshold Determination Methods

- Formula: Fmax ≈ 0.35/tr (tr = rise time in ns)

- Wavelength calculation: λ = Vp/Fmax (Vp = propagation velocity in mm/ns)

- FR4 propagation velocity: ~150mm/ns (√(c²/εr), εr=4.5)

- Practical test: TDR (Time Domain Reflectometry) for impedance discontinuity detection

4. Signal Integrity

Key Integrity Metrics

- Return loss: ≥-15dB (up to 25Gbps); ≥-20dB (50Gbps+)

- Jitter: ≤10% of bit period (e.g., ≤20ps for 50Gbps)

- Eye diagram: BER (Bit Error Rate) ≤1e-12 for high-reliability applications

- Ground bounce: ≤50mV (simultaneous switching of 16 outputs)

Integrity Preservation Techniques

- Termination: Series (47–50Ω), parallel, or Thevenin termination

- Decoupling capacitors: 0.1μF (X7R) + 10μF (tantalum) within 50mil of IC power pins

- Reference plane continuity: No splits under high-speed traces (loop area <100mm²)

- Pre-emphasis and equalization: Compensates for insertion loss in >25Gbps paths

Learn more about: Signal Integrity in HDI PCB Design

5. Transmission Line Behavior

Line Types and Properties

- Microstrip: Signal layer + adjacent ground plane (impedance formula: Z0 = 60/√εr × ln(4h/(0.67π(0.8w+t))))

- Stripline: Signal layer between two ground planes (Z0 = 60/√εr × ln(1.9h/(0.8w+t)))

- Differential pairs: Edge-coupled (Zdiff ≈ 2×Z0(1–0.48e^(-0.96d/h)))

- Characteristic impedance variables: Trace width (w), dielectric height (h), copper thickness (t), εr

Behavior Management

- Impedance control: Trace width adjustment (3mil = 50Ω on 4mil FR4)

- Stub reduction: Backdrilling to eliminate stubs >5mil (25Gbps+)

- Serpentine tuning: Length matching ±1mil for differential pairs

- Cross-talk mitigation: Orthogonal routing on adjacent layers

6. Design Constraints

Dimensional and Geometric Limits

- Trace/space: Minimum 2.5mil/2.5mil (outer layers); 2mil/2mil (inner layers, hdi pcb)

- Annular ring: ≥2mil (outer layers, IPC-6012 Class 3); ≥1.5mil (inner layers)

- Via pitch: ≥0.5mm (microvias); ≥1mm (through-hole vias)

- Board edge clearance: 15mil (traces); 20mil (vias)

Manufacturing Constraints

- Aspect ratio: Through-hole vias ≤10:1; microvias ≤0.75:1

- Copper weight: 1–2oz (balances current capacity and impedance control)

- Dielectric thickness tolerance: ±10% (critical for impedance consistency)

- Panelization: V-score or mouse bites ≥10mil from copper features

Learn more about: How to Design HDI Microvia PCB

7. Material Selection

Low Loss vs. Ultra Low Loss Options

| Material | Dk @10GHz | Df @10GHz | Tg (°C) | Application |

|---|---|---|---|---|

| FR408HR | 3.48–3.67 | 0.0093–0.0098 | 180 | General high speed pcb |

| Isola I-Speed | 3.45–3.55 | 0.0059 | 180 | Low Loss PCB (≤50Gbps) |

| Rogers 4350B | 3.48 | 0.0017 | 180 | ultra low loss pcb (≥50Gbps) |

| Astra MT77 | 2.95–3.01 | 0.0017–0.0019 | 200 | 60–100GHz high speed pcb |

Material Compatibility and Selection

- CTE matching: Core/buildup layers ≤3ppm/°C difference (reduces microvia cracking)

- Moisture absorption: ≤0.15% (prevents delamination during reflow)

- Thermal conductivity: ≥0.3W/m·K (FR4); ≥0.6W/m·K (high-performance materials)

- Cost-benefit: ultra low loss pcb costs 3–4x FR4 but reduces insertion loss by 50%

8. Material and Stackup

Stackup Design Principles

- Symmetric structure: Signal-GND-Power-GND-Signal (4-layer); 2+N+2 (hdi pcb)

- Dielectric thickness: 4mil (signal-reference plane); 8–12mil (core layers)

- Power plane placement: Adjacent to ground plane (capacitance ≥0.5pF/cm²)

- High-speed layer assignment: Critical signals on inner layers (stripline) for shielding

Early Fabrication Involvement

- Stackup validation: Confirm lamination cycles (max 4 for sequential HDI)

- Material availability: Verify lead times for ultra low loss materials (4–6 weeks)

- Drill capability check: Minimum 0.1mm microvia diameter

- Test coupon inclusion: Impedance (50Ω/100Ω) and thermal cycling test structures

9. Surface Finish and Testing

Finishes for High-Speed Performance

- ENIG: Ni 3–6μm, Au 0.05–0.15μm (general high speed pcb)

- ENEPIG: Ni 3–6μm, Pd 0.1–0.2μm, Au 0.05μm (fine-pitch hdi pcb)

- Immersion Silver: 0.8–1.2μm (cost-effective Low Loss PCB)

- Compliance: IPC-4552 (ENIG), IPC-4556 (ENEPIG)

Testing Requirements

- Impedance testing: TDR ±2% tolerance

- Signal integrity: Eye diagram analysis (10Gbps+); BER testing

- Thermal cycling: -40°C to 125°C, 1000 cycles (no microvia cracking)

- X-ray inspection: 100% via fill (≥98%) and annular ring verification

10. Fabrication Guidelines

Annular Rings and Board Edge

- Outer layer annular ring: ≥2mil (Class 2); ≥3mil (Class 3)

- Inner layer annular ring: ≥1.5mil (Class 2); ≥2mil (Class 3)

- Board edge clearance: 15mil (traces); 20mil (vias); 50mil (high-speed differential pairs)

- Depaneling: Laser or V-score (10mil from copper features)

Data Package Standards

- Gerber X2 files: Complete layer set (signal, power, ground, mask, silk)

- Drill files: NC drill + rout files with via classification (microvia/through-hole)

- Supporting documents: Stackup diagram, impedance table, IPC class specification

- Netlist and DFM report: Pre-production validation of manufacturability

11. 3W Rule

Implementation Details

- Rule definition: Trace center-to-center spacing ≥3× trace width

- Application: Reduces crosstalk by 20–25dB in high-speed designs

- Adjustments: 5W rule for differential pairs; 8–10W for clock signals

- Calculation example: 3mil trace → 9mil center-to-center spacing

Exceptions and Optimization

- Dense hdi pcb: Minimum 2× width (crosstalk ≤-30dB)

- Layer-specific: Orthogonal routing on adjacent layers reduces broadside crosstalk

- Simulation validation: 3D field solver for critical nets (e.g., 50Gbps SerDes)

- Ground plane separation: ≤10mil between signal and ground layers enhances 3W effectiveness

12. Key Comparison Tables

High-Speed vs. Standard PCB

| Aspect | High Speed PCB | Standard PCB |

|---|---|---|

| Signal Speed | ≥1Gbps | ≤100Mbps |

| Impedance Control | ±5% | ±10% |

| Trace/Space | 2.5/2.5mil | 4/4mil |

| Material Df | ≤0.006 | ≤0.015 |

| Manufacturing Tolerance | ±1mil | ±2mil |

Microstrip vs. Stripline

| Aspect | Microstrip | Stripline |

|---|---|---|

| Layers Required | 2+ | 3+ |

| Propagation Delay | ~5ns/m | ~6ns/m |

| EMI Radiation | Higher | Lower |

| Impedance Control | Easier | More complex |

| Cost | Lower | Higher |

Factory Case Study

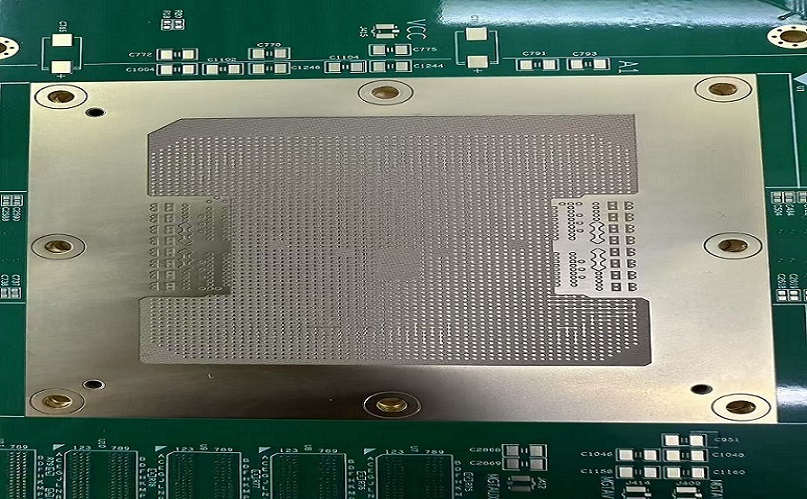

16-Layer HDI High Speed PCB for 25Gbps Data Center

Project Specifications

- Layer structure: 2+12+2 hdi pcb stackup (16-layer high speed pcb)

- Materials: Isola I-Speed (Low Loss PCB), Tg 180°C, Dk 3.45, Df 0.0059

- Parameters: 50Ω single-ended, 100Ω differential; 3mil/3mil trace/space; 0.12mm microvias

- Application: 25Gbps Ethernet switch (data center)

Issues Encountered

- Annular ring 1.5mil (outer layers) caused 22% via breakout during drilling

- Unstitched ground planes led to crosstalk >-28dB (failed IPC Class 3)

- Via stubs >8mil resulted in return loss < -12dB @25GHz

- Material moisture absorption (0.2%) caused delamination during reflow

Improvements Implemented

- Increased annular ring to 3mil (outer layers) and 2mil (inner layers)

- Added stitching vias (0.2mm diameter, 100mil spacing) to ground planes

- Backdrilled through-hole vias to eliminate stubs >5mil

- Selected low-moisture material (<0.15%) and pre-baked before lamination

- Conducted pre-layout DFM review with fabrication team

Results

- Yield improved from 68% to 93%

- Crosstalk reduced to -38dB (meets IPC Class 3)

- Return loss ≥-18dB @25GHz

- Thermal cycle failure rate (1000 cycles) reduced from 18% to 1.5%

- Production lead time shortened by 12 days

Common Design Errors

- Ignoring critical length: Traces >2 inches (FR4) for 1ns rise time without transmission line design.

- Inadequate annular rings: <1.5mil (outer layers) leading to via breakout and open circuits.

- Split ground planes: Creates large current loops (>200mm²) and EMI >40dBμV/m.

- Overlooking via stubs: Unbackdrilled vias with stubs >5mil cause impedance discontinuities.

- Material mismatch: Using standard FR4 (Df=0.015) for >25Gbps signals (insertion loss >0.5dB/inch).

- Violation of 3W rule: Trace spacing <3× width leading to crosstalk >-30dB.

- Poor decoupling: Capacitors placed >100mil from IC power pins (ground bounce >100mV).

- Unsymmetric stackup: Causes warpage >0.8mm/m (assembly alignment issues).

FAQ

1. When should I use ultra low loss pcb instead of Low Loss PCB?

ultra low loss pcb (Df ≤0.002) is required for data rates ≥50Gbps, trace lengths >6 inches, or frequencies >20GHz. Low Loss PCB (Df 0.003–0.006) is cost-effective for 25–50Gbps signals or shorter trace lengths, balancing performance and manufacturing costs.

2. How to verify high speed pcb signal integrity before production?

Use 3D field solver tools for impedance and crosstalk simulation, generate test coupons for impedance validation (TDR), perform eye diagram analysis for high-speed interfaces, and conduct thermal cycling simulations to predict reliability. Pre-production prototypes with TDR and BER testing confirm real-world performance.

3. What are the key fabrication requirements for hdi pcb high speed designs?

hdi pcb high speed designs require laser drilling for 0.1–0.15mm microvias, sequential lamination (max 4 cycles), copper-filled via-in-pad (≥98% fill), impedance testing ±2% tolerance, and X-ray inspection for via integrity. Compliance with IPC-6012 Class 3 and IPC-2226 is mandatory for high-reliability applications.

If you need high speed PCB manufacturing or design support,our engineering team provides free DFM analysis and quotation.

![Understanding PCB Costs & Pricing [Your Complete Guide] Understanding PCB Costs & Pricing [Your Complete Guide]](https://hdicircuitboard.com/wp-content/uploads/elementor/thumbs/Understanding-PCB-Costs-Pricing-Your-Complete-Guide-qzzhe6mcaxuolkux3xalfktgavumi9y1aqfbs9bpv4.webp)