High-speed PCB material selection directly dictates signal integrity, manufacturing yield, and long-term reliability—especially for hdi pcb, Low Loss PCB, and ultra low loss pcb applications. This guide breaks down key material properties (Dk/Df, Tg, CAF resistance), compares mainstream laminates (FR-4, PTFE, hydrocarbon), and provides factory-proven selection criteria aligned with IPC standards and real-world production constraints.

Learn more about: What Is High-Speed PCB? A Comprehensive Guide

Technical Points

1. High-speed PCB Materials

Core Material Properties

- Dielectric Constant (Dk): Stable ±0.1 @10GHz (critical for impedance control ±5%)

- Dissipation Factor (Df): ≤0.006 (Low Loss PCB); ≤0.002 (ultra low loss pcb)

- Glass Transition Temperature (Tg): ≥135°C (standard); ≥170°C (automotive/industrial hdi pcb)

- CAF Resistance: IPC-TM-650 2.6.25 Class 3 (no conductive anodic filament growth at 85°C/85% RH)

- Thermal Decomposition Temperature (Td): ≥320°C (compatible with lead-free reflow 260°C peak)

Material Classification by Performance

- Standard FR-4: Dk 4.2–4.5 @10GHz, Df 0.012–0.018 (≤1Gbps high speed pcb)

- High-Speed Laminates: Dk 3.4–3.8 @10GHz, Df 0.005–0.008 (1–25Gbps, Low Loss PCB)

- Ultra Low Loss: Dk 2.9–3.3 @10GHz, Df ≤0.002 (≥25Gbps, ultra low loss pcb)

- HDI-Optimized: Low CTE (X/Y ≤16ppm/°C) for microvia reliability (0.1–0.15mm diameter)

2. High-Speed PCB vs. Normal PCB Materials

Key Property Differences

| Aspect | High Speed PCB | Normal PCB |

|---|---|---|

| Dk Stability | ±0.1 @10GHz | ±0.3 @1GHz |

| Df @10GHz | ≤0.006 | ≤0.018 |

| Tg Minimum | 170°C | 135°C |

| CAF Resistance | IPC Class 3 | IPC Class 1/2 |

| CTE X/Y | ≤16ppm/°C | ≤20ppm/°C |

Manufacturing Impact

- High speed pcb: Tighter dielectric thickness tolerance (±10% vs. ±15% for normal PCB)

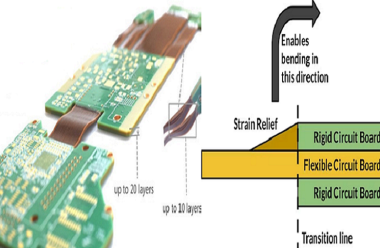

- hdi pcb: Sequential lamination compatible (max 4 cycles) vs. 2 cycles for normal PCB

- ultra low loss pcb: Laser drilling only (0.1mm microvias) vs. mechanical drilling for normal PCB

- Impedance control: ±2% (high speed pcb) vs. ±10% (normal PCB) per IPC-6012

3. High-Speed PCB Material Comparison

Material Performance Matrix

| Material Type | Dk @10GHz | Df @10GHz | Tg (°C) | CAF Resistance | Cost vs. FR-4 | Best For |

|---|---|---|---|---|---|---|

| Standard FR-4 | 4.2–4.5 | 0.012–0.018 | 135–150 | Class 1 | 1x | ≤1Gbps high speed pcb |

| High-Speed FR-4 (FR408HR) | 3.48–3.67 | 0.0093–0.0098 | 180 | Class 2 | 1.5x | 1–10Gbps hdi pcb |

| PTFE/Ceramic (Rogers 4350B) | 3.48 | 0.0017 | 180 | Class 3 | 4x | ≥25Gbps ultra low loss pcb |

| PPE/PPO Hydrocarbon (Megtron 7) | 3.38 | 0.0025 | 200 | Class 3 | 3x | 10–50Gbps Low Loss PCB |

| PPE/PPO Hydrocarbon (Megtron 8) | 3.28 | 0.0019 | 220 | Class 3 | 5x | ≥50Gbps ultra low loss pcb |

Learn more about: Materials for HDI PCB: Full Classification Guide

Material-Specific Characteristics

- Standard FR-4: Cost-effective but high loss; limited to low-speed high speed pcb (≤1Gbps)

- High-Speed Laminates (FR408HR): Balanced performance for mid-range hdi pcb (1–10Gbps)

- PTFE/Ceramic-Filled PTFE: Ultra-low loss but high cost; requires specialized lamination for hdi pcb

- PPE/PPO Hydrocarbon: High Tg + low loss; ideal for automotive/industrial Low Loss PCB (10–50Gbps)

4. Material Selection Factors

Electrical & Thermal Requirements

- Data rate matching: 1–10Gbps → High-Speed FR-4; ≥25Gbps → ultra low loss pcb (PTFE/hydrocarbon)

- Temperature range: -40°C to 125°C → Tg ≥170°C (automotive hdi pcb)

- Impedance target: 50Ω (single-ended) → Dk 3.4–3.8; 100Ω (differential) → Dk 2.9–3.3

- Thermal cycling: 1000 cycles (-40°C/125°C) → CAF Resistance Class 3

Manufacturing & Cost Constraints

- Lamination compatibility: Sequential lamination (hdi pcb) → PPE/PPO (vs. PTFE’s poor bond strength)

- Drillability: Microvias (0.1–0.15mm) → Laser-drillable materials (hydrocarbon/FR408HR)

- Cost balance: ultra low loss pcb (PTFE) = 4–5x FR-4; Low Loss PCB (hydrocarbon) = 3x FR-4

- Lead time: PTFE (6–8 weeks) vs. High-Speed FR-4 (2–3 weeks) for hdi pcb production

5. Common Material Recommendations

Application-Specific Selections

- Consumer Electronics (smartphones): hdi pcb → High-Speed FR-4 (FR408HR), Tg 180°C

- Data Center (25Gbps): Low Loss PCB → Megtron 7 (PPE/PPO), Df 0.0025

- Aerospace/Defense (50Gbps): ultra low loss pcb → Rogers 4350B (PTFE), Df 0.0017

- Automotive ADAS: hdi pcb → Megtron 8 (PPE/PPO), Tg 220°C, CAF Class 3

HDI-Specific Recommendations

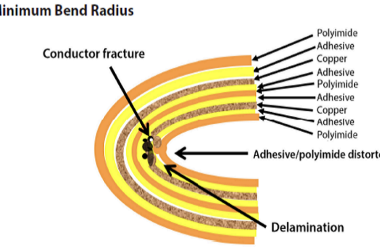

- Microvia aspect ratio ≤0.75:1 → Materials with low CTE (≤16ppm/°C)

- Via-in-Pad (VIP) → Copper-filled compatible (hydrocarbon/FR408HR vs. PTFE)

- Sequential lamination → No PTFE (poor interlayer adhesion); use PPE/PPO or high-speed FR-4

- Trace/space 2.5/2.5mil → Dielectric thickness 4mil (impedance 50Ω)

6. Early Fabrication Involvement

Pre-Design Validation

- Material availability check: ultra low loss pcb (Megtron 8) lead time 4–6 weeks

- Lamination cycle review: hdi pcb sequential lamination (max 4 cycles) compatibility

- Drill capability verification: Laser drilling for 0.1mm microvias (PTFE/hydrocarbon)

- Test coupon design: Include impedance (50Ω/100Ω) and thermal cycling structures

DFM Alignment

- Material thickness tolerance: ±10% (critical for impedance control in high speed pcb)

- Copper weight matching: 1oz outer/0.5oz inner (balances flexibility for hdi pcb)

- Reflow profile validation: 260°C peak (compatible with Tg ≥170°C materials)

- Pre-bake requirements: 125°C for 4 hours (moisture content ≤0.15% for hdi pcb)

7. Surface Finish and Testing

Finishes for High-Speed Materials

- ENIG: Ni 3–6μm, Au 0.05–0.15μm (general high speed pcb/hdi pcb)

- ENEPIG: Ni 3–6μm, Pd 0.1–0.2μm, Au 0.05μm (ultra low loss pcb fine-pitch BGAs)

- Immersion Silver: 0.8–1.2μm (cost-effective Low Loss PCB)

- Compliance: IPC-4552 (ENIG), IPC-4556 (ENEPIG)

Material Quality Testing

- Dk/Df Verification: Vector Network Analyzer (VNA) @10GHz (±0.01 Dk, ±0.0005 Df)

- Thermal Cycling: -40°C to 125°C, 1000 cycles (no microvia cracking in hdi pcb)

- CAF Testing: IPC-TM-650 2.6.25 (1000 hours @85°C/85% RH, no failure)

- Impedance Testing: TDR ±2% tolerance (50Ω single-ended, 100Ω differential)

8. Fabrication Guidelines

Annular Rings & Board Edge

- Outer layer annular ring: ≥2mil (Class 2); ≥3mil (Class 3) for high speed pcb

- Inner layer annular ring: ≥1.5mil (Class 2); ≥2mil (Class 3) for hdi pcb

- Board edge clearance: 15mil (traces); 20mil (vias) for ultra low loss pcb

- Depaneling: Laser depaneling (vs. V-score) for ultra low loss pcb (reduces edge stress)

Data Package Requirements

- Gerber X2 files: Layer stack with material type/thickness per layer

- Material spec sheet: Dk/Df, Tg, CTE, and CAF resistance data

- Fabrication notes: IPC class (2/3), surface finish, and microvia specifications (0.1–0.15mm)

- Test plan: Impedance, thermal cycling, and CAF testing requirements

9. Key Comparison Tables

Megtron 7 vs. Megtron 8 (Ultra Low Loss PCB)

| Aspect | Megtron 7 | Megtron 8 |

|---|---|---|

| Dk @10GHz | 3.38 | 3.28 |

| Df @10GHz | 0.0025 | 0.0019 |

| Tg (°C) | 200 | 220 |

| Cost vs. FR-4 | 3x | 5x |

| Max Data Rate | 50Gbps | 112Gbps |

PTFE vs. PPE/PPO Hydrocarbon (Low Loss PCB)

| Aspect | PTFE/Ceramic | PPE/PPO Hydrocarbon |

|---|---|---|

| Df @10GHz | 0.0017 | 0.0019–0.0025 |

| CAF Resistance | Class 3 | Class 3 |

| HDI Compatibility | Poor (adhesion) | Excellent |

| Manufacturing Cost | 4x FR-4 | 3x FR-4 |

| Lead Time | 6–8 weeks | 4–6 weeks |

Factory Case Study

12-Layer HDI Ultra Low Loss PCB for 50Gbps Telecom

Project Specifications

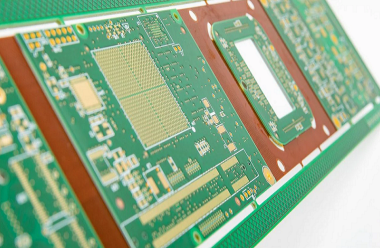

- Layer structure: 2+8+2 hdi pcb stackup (12-layer high speed pcb)

- Materials: Megtron 7 (Low Loss PCB), Tg 200°C, Dk 3.38, Df 0.0025

- Parameters: 50Ω single-ended, 100Ω differential; 3mil/3mil trace/space; 0.12mm microvias

- Application: 50Gbps telecom transceiver (ultra low loss pcb requirement)

Issues Encountered

- Incorrect material selection (standard FR-4 instead of Megtron 7) → insertion loss >0.5dB/inch @20GHz

- CAF failure (IPC Class 2 material) → 18% open circuits after 500 thermal cycles

- Microvia cracking (CTE mismatch 5ppm/°C) → 22% yield loss

- Dielectric thickness tolerance ±15% → impedance variation ±8% (failed IPC Class 3)

Improvements Implemented

- Switched to Megtron 7 (Low Loss PCB) → insertion loss reduced to 0.2dB/inch @20GHz

- Upgraded to IPC Class 3 CAF-resistant material → 0% CAF failures

- Matched core/buildup CTE (≤2ppm/°C difference) → microvia cracking <1%

- Tightened dielectric tolerance to ±10% → impedance variation ±2% (meets Class 3)

- Pre-production DFM review with fabrication team (early material validation)

Results

- Yield improved from 65% to 94%

- Insertion loss reduced by 60% (0.2dB/inch @20GHz)

- Thermal cycle failure rate (1000 cycles) reduced from 22% to 1%

- Impedance compliance rate 100% (IPC Class 3)

- Production lead time optimized by 10 days (early material alignment)

Common Design Errors

- Using standard FR-4 for >10Gbps signals (Df too high → insertion loss >0.5dB/inch @20GHz)

- Ignoring CAF resistance (IPC Class 1 material) → 18% open circuits in hdi pcb after environmental testing

- CTE mismatch (>3ppm/°C) between core/buildup layers → microvia cracking in ultra low loss pcb

- Inadequate annular rings (<1.5mil) → 25% via breakout during drilling for high speed pcb

- Late material validation → 4–6 week delays for ultra low loss pcb (Megtron 8) availability

- Overlooking dielectric thickness tolerance (±15%) → impedance variation ±8% (failed Class 3)

- Using PTFE for sequential lamination hdi pcb → poor interlayer adhesion (15% delamination)

- Missing material spec in data package → misfabrication (wrong Dk material for impedance target)

FAQ

1. When should I choose ultra low loss pcb over Low Loss PCB for hdi pcb?

ultra low loss pcb (Df ≤0.002) is required for data rates ≥25Gbps, trace lengths >6 inches, or frequencies >20GHz in hdi pcb designs. Low Loss PCB (Df 0.003–0.006) is cost-effective for 1–25Gbps signals, balancing performance and manufacturing costs for most hdi circuit boards.

2. How to validate high speed pcb material performance before production?

Conduct pre-production testing with test coupons: verify Dk/Df via VNA @10GHz, perform thermal cycling (-40°C/125°C, 1000 cycles) for microvia reliability, test CAF resistance per IPC-TM-650, and validate impedance with TDR (±2% tolerance). Early collaboration with fabricators confirms material manufacturability for hdi pcb.

3. What are the key fabrication constraints for ultra low loss pcb (PTFE/hydrocarbon)?

ultra low loss pcb requires laser drilling (0.1–0.15mm microvias), tight dielectric thickness tolerance (±10%), laser depaneling (reduces edge stress), and specialized lamination (low pressure for PTFE) to avoid delamination. For hdi pcb, PPE/PPO hydrocarbon is preferred over PTFE for sequential lamination compatibility.

If you need high speed PCB manufacturing or design support,our engineering team provides free DFM analysis and quotation.

![Understanding PCB Costs & Pricing [Your Complete Guide] Understanding PCB Costs & Pricing [Your Complete Guide]](https://hdicircuitboard.com/wp-content/uploads/elementor/thumbs/Understanding-PCB-Costs-Pricing-Your-Complete-Guide-qzzhe6mcaxuolkux3xalfktgavumi9y1aqfbs9bpv4.webp)