Microvia HDI PCB represents the foundation of modern high-density interconnect technology, using laser-drilled vias ≤150μm with aspect ratio ≤1:1, sequential lamination, and stacked/staggered configurations to enable miniaturization, superior signal integrity, and high-component-density designs. This factory-verified guide covers definitions, via types, stackup structures, manufacturing processes, reliability controls, and application-specific design rules aligned with IPC-2226 and IPC-6012.

Learn more about: What’s HDI? Design Basics and Complete HDI PCB Manufacturing Process

Microvia HDI PCB: Official Definition & Core Structure

IPC-Standard Definition

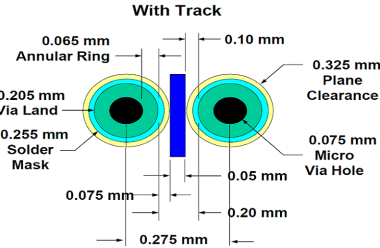

Microvia HDI PCB is a high-density interconnect circuit board defined by IPC-2226 and IPC-2315, featuring:

- Laser-drilled microvias with finished hole diameter ≤150μm (6mil)

- Aspect ratio (depth/diameter) ≤1:1, optimal ≤0.75:1

- Dielectric thickness ≤0.25mm per microvia layer

- Fine-line traces ≤100μm (4mil) and high pad density >20 pads/cm²

- Blind, buried, stacked, or staggered via structures

Fundamental Structural Principle

Microvias replace large through-hole vias to connect only adjacent layers, shortening electrical paths, eliminating stub reflections, and freeing routing space. Sequential lamination builds up layers incrementally, enabling stacked and staggered configurations impossible in standard PCBs.

Key Aspects of Microvias

Definition & Structure

- Diameter range: 50–150μm (2–6mil) in mass production

- Conical shape: Top diameter ~15% larger than bottom for reliable plating

- Copper plating thickness: 15–20μm minimum for structural integrity

- Capture pad: 300–400μm for 100μm microvias (IPC-2221)

- Aspect ratio: ≤1:1 to ensure void-free plating

Types

Single Microvia

- Connects one outer layer to one adjacent inner layer

- Diameter: 75–125μm, aspect ratio ≤0.75:1

- Used in 1+N+1 first-order HDI structures

- Most reliable microvia configuration (yield >98%)

Stacked Vias

- Vertically aligned microvias forming a continuous vertical path

- Up to 3 stacked microvias in production

- Requires copper filling and planarization between layers

- Saves 60% lateral space vs staggered vias

Staggered Vias

- Horizontally offset microvias between layers

- Offset distance ≥50μm to prevent shorting

- No copper filling required between layers

- Preferred for high-reliability applications (automotive, aerospace)

Skipped Vias

- Single laser drill spanning two dielectric layers

- Aspect ratio ≤0.8:1, advanced process capability

- Eliminates intermediate landing pads

- Reduces layer count by 1–2 layers in complex designs

Key Features and Benefits of Microvia HDI PCB

High-Density Interconnect

- Pad density: ≥20 pads/cm², 3x standard PCB

- Supports 0.3–0.5mm pitch BGA components

- Trace width/spacing: 75/75μm (3mil) minimum

- Routing density: 4x higher than conventional designs

Space Savings

- 30–50% smaller footprint than standard PCB

- 25–40% thinner profile (down to 0.4mm)

- Eliminates through-hole via land pads

- Enables 0.3mm pitch component placement

Signal Integrity

- Signal path length reduced by 60–80%

- Parasitic inductance reduced by 50–70%

- Insertion loss improved by 25–35% at 10GHz+

- Impedance stability: ±5% (IPC-2221 Class 3)

- Elimination of via stub reflections

Learn more about : When to Choose High Density Interconnect (HDI) PCBs Over Conventional Printed Circuit Boards

Common HDI Microvia Configurations

1+N+1 HDI Structure

- 1 build-up layer each side of core

- Single lamination cycle

- Single-level microvias (L1–L2, Ln–Ln-1)

- Total layers: 4–12 typical

- Application: Consumer electronics, wearables

2+N+2 HDI Structure

- 2 build-up layers each side of core

- 2 sequential lamination cycles

- Stacked/staggered microvias (L1–L3)

- Total layers: 8–16 typical

- Application: 5G modules, automotive ADAS

Stacked vs. Staggered Vias

| Parameter | Stacked Vias | Staggered Vias |

|---|---|---|

| Space Usage | Minimal (vertical alignment) | Moderate (horizontal offset) |

| Processing Complexity | High (copper fill required) | Low (no filling needed) |

| Manufacturing Yield | 91–94% | 96–98% |

| Reliability | Good | Excellent |

| Best For | Ultra-dense routing | High-reliability systems |

Microvia HDI PCB vs. Standard PCB

| Parameter | Standard PCB | Microvia HDI PCB |

|---|---|---|

| Via Diameter | ≥300μm | 50–150μm |

| Aspect Ratio | Up to 10:1 | ≤1:1 |

| Trace Width | ≥150μm | ≤100μm |

| Layer Count | High | 30–50% Lower |

| Signal Integrity | Standard | Superior |

Learn more about : How to Choose Between Microvias, Stacked Vias, and Staggered Vias for High Density Interconnect (HDI) PCBs

Benefits of Microvia HDI PCB

Electrical Performance Advantages

- Reduced loop inductance: 50–70% lower

- Improved return loss: 10–15dB better

- Lower crosstalk: 20–30% reduction

- Enhanced EMI suppression

- Superior high-speed performance up to 112Gbps

Mechanical & Manufacturing Advantages

- Thinner board profile: 25–40% reduction

- Improved thermal dissipation

- Higher assembly yield for fine-pitch components

- Reduced layer count: 30–50% fewer layers

- Greater design flexibility

Applications

Consumer Electronics

- Smartphones, tablets, wearables

- VR/AR headsets, portable devices

- Miniaturized IoT sensors

- Camera modules and compact controllers

Advanced Networking

- 5G/6G small cells and base stations

- 10G/25G/100G Ethernet modules

- High-speed routers and switches

- Optical transceiver interfaces

Industrial/Automotive

- Automotive ADAS and infotainment

- EV battery management systems

- Industrial automation controllers

- High-temperature sensors (–40°C to 150°C)

Manufacturing Considerations

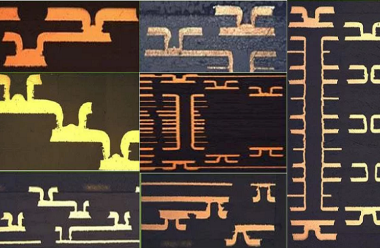

Drilling

- Laser type: UV laser (355nm) for precision microvias

- Drill accuracy: ±15μm position control

- Depth tolerance: ±5μm for consistent aspect ratio

- Desmear process: Plasma treatment for adhesion

- Microvia drilling rate: 10,000–20,000 holes per second

Plating

- Copper plating thickness: ≥15μm uniform coverage

- Void requirement: ≤2% void area (IPC-6012 Class 3)

- Filling material: Epoxy-copper paste for stacked vias

- Planarization: Surface planarity ≤5μm for stacked vias

- Plating uniformity: ±5% across entire panel

Reliability

- Thermal cycling: 1000 cycles (–40°C to 125°C)

- Humidity resistance: 85°C/85% RH, 500 hours

- Resistance to thermal shock: 100 cycles

- Pull strength: ≥1.5kgf per microvia

- Compliance: IPC-6016 HDI performance standard

Core Technical Parameters

- Microvia diameter: 50–150μm (2–6mil)

- Aspect ratio: ≤1:1 (design rule ≤0.75:1)

- Trace width/spacing: 75–100μm (3–4mil)

- Dielectric thickness: 50–100μm per layer

- Impedance tolerance: ±5% (50Ω single-ended)

- Registration accuracy: ±30μm layer-to-layer

- Warpage limit: ≤0.2mm/m

Case Study

Project Specifications

- Type: 2+8+2 HDI microvia PCB

- Layers: 12 total

- Microvias: 100μm stacked (2 levels)

- Trace width: 75μm (3mil)

- Application: 5G automotive telematics module

Issues Encountered

- Stacked via registration error ±40μm

- Microvia voiding in 8% of vias

- Trace etching tolerance ±15μm out of spec

- Warpage 0.35mm/m exceeding limits

Improvements Implemented

- Laser drilling calibration to ±20μm

- Optimized plating current profile

- Etch factor compensation for fine lines

- Symmetric stack-up and lamination profile

- Aspect ratio reduced to 0.75:1

Results

- Registration accuracy ±25μm (in spec)

- Microvia voiding eliminated (0%)

- Trace tolerance stabilized to ±8μm

- Warpage controlled to 0.18mm/m

- Manufacturing yield improved from 76% to 95.8%

- Module size reduced by 32%

Common Design Errors

- Aspect ratio violation: >1:1 causes plating voids and 10–20% yield loss

- Insufficient stacked via filling: BGA pad dimpling >25μm causes solder defects

- Staggered via offset <50μm: Results in short circuits and rework

- Capture pad undersized: <2.5x via diameter causes connection failures

- Unbalanced stack-up: Creates warpage >0.3mm/m leading to assembly failure

Quality Control & Compliance

Testing Protocols

- Microvia cross-section analysis: Void percentage <2%

- Impedance testing: TDR measurement per IPC-TM-650

- Automated optical inspection: 100% via and trace coverage

- Laser drill verification: Diameter and position accuracy

- Interconnect Stress Testing (IST): 500 cycles minimum

Standards Compliance

- IPC-2226: HDI PCB design standard

- IPC-2315: Microvia design guidelines

- IPC-6012/6016: Rigid HDI PCB performance

- IPC-4104: HDI laminate requirements

- ISO 9001: Manufacturing quality system

FAQ

Q1: What defines a microvia in HDI PCB per IPC standards?

A1: IPC defines a microvia as a laser-drilled via with diameter ≤150μm, aspect ratio ≤1:1, connecting only adjacent layers in an HDI PCB structure.

Q2: What is the difference between stacked and staggered microvias?

A2: Stacked vias align vertically for minimal space; staggered vias offset horizontally for easier manufacturing and higher reliability in hdi pcb manufacturing.

Q3: What does 1+N+1 mean in microvia HDI PCB?

A3: 1+N+1 indicates one build-up layer on each side of a central core, using single-level microvias and one lamination cycle in hdi pcb fabrication.

Q4: What reliability tests apply to microvia HDI PCB?

A4: Microvia HDI PCB requires thermal cycling (–40°C to 125°C), IST testing, cross-section analysis, and impedance verification per IPC-6016 Class 3.

If you need HDI PCB manufacturing or design support, our engineering team provides free DFM analysis and quotation.

Learn more about: How Does High Density Interconnect (HDI) Affect BGA Fanout and Component Placement?

![Understanding PCB Costs & Pricing [Your Complete Guide] Understanding PCB Costs & Pricing [Your Complete Guide]](https://hdicircuitboard.com/wp-content/uploads/elementor/thumbs/Understanding-PCB-Costs-Pricing-Your-Complete-Guide-qzzhe6mcaxuolkux3xalfktgavumi9y1aqfbs9bpv4.webp)