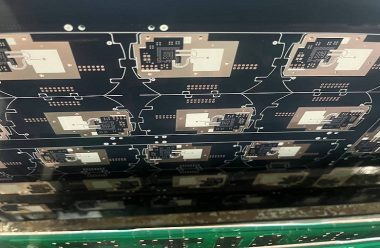

High speed PCB routing demands precision in reference plane design, impedance control, and component placement to mitigate crosstalk, EMI, and signal degradation—critical for hdi pcb, Low Loss PCB, and ultra low loss pcb applications. This guide distills factory-proven practices, actionable parameters, and real-world insights to ensure robust performance in high-frequency (≥1Gbps) designs.

Learn more about: What Is High-Speed PCB? A Comprehensive Guide

High Speed PCB Design Requires: Foundational Principles

Speed Threshold & Design Scope

- Classify high-speed signals by edge rate (≥1V/ns) or data rate (≥1Gbps) per IPC-2221 standard.

- Mandate controlled impedance routing for signals exceeding 3Gbps (e.g., PCIe 5.0, 5G mmWave).

- Prioritize ultra low loss pcb materials (Df ≤0.002 @10GHz) for data rates ≥25Gbps.

Non-Negotiable Design Prerequisites

- Layer stackup approval from fabricators before routing (minimum 4 layers for high speed pcb).

- Pre-routing simulation of signal integrity (SI) and power integrity (PI) using field solvers.

- Compliance with IPC-6012 Class 3 for high-reliability applications (aerospace, medical).

Reference Planes: Low-Impedance Return Paths

Plane Design Specifications

- Use solid ground planes for all high-speed signal layers (gap ≤50mil per IPC-2226).

- Maintain plane continuity under differential pairs—splits cause 10x higher crosstalk.

- Implement stitching vias (1mm pitch) along plane edges to reduce loop inductance.

Plane Pair Optimization

- Space power and ground planes ≤0.2mm to leverage inherent capacitance (32.7pF/in² for FR-4).

- For hdi circuit boards, assign dedicated ground planes adjacent to signal layers (1+N+1 stackup).

- Avoid routing over plane slots; use 10nF–100nF stitching capacitors if unavoidable.

| Plane Configuration | Signal Integrity Impact | Best For |

|---|---|---|

| Solid Ground Plane | -35dB crosstalk reduction | High speed pcb (≥10Gbps) |

| Split Ground Plane | +20dB EMI radiation | Low-speed non-critical signals |

Controlled Impedance: Precision Routing

Impedance Targets & Tolerances

- Single-ended traces: 50Ω ±5% (microstrip) or 75Ω ±7% (RF applications).

- Differential pairs: 90–100Ω ±5% (IPC-2221), critical for ultra low loss pcb designs.

- Calculate trace dimensions using Polar Si9000: 4mil width for 50Ω on 0.4mm FR-4 (h=0.2mm).

Manufacturing Compatibility

- Account for etch variation (±0.5mil) when defining trace widths.

- Use impedance coupons (100mm length) on every panel for TDR testing.

- Match dielectric constant (εr) tolerance: ±0.05 for ultra low loss pcb materials.

Differential Pair Routing: Symmetry & Timing

Routing Rules with Specific Values

- Maintain consistent spacing (4–6mil) and width (4mil) along the entire pair length.

- Length mismatch ≤5mil (≤25ps skew) for signals ≥10Gbps.

- Route pairs on the same layer; cross-layer transitions need equal via counts (max 2 vias/pair).

Pair Protection & Isolation

- Keep differential pairs 3x pair spacing away from other traces (3W rule extension).

- Place AC coupling capacitors (0402 package) symmetrically within 50mil of the source.

- Avoid T-junctions in pairs—use daisy-chain topology for multi-drop interfaces.

Learn more about: Controlled Impedance in High-Speed PCB: Full Tutorial

Via Usage: Minimizing Parasitics

Via Design Parameters

- Microvias (0.1–0.15mm diameter) for hdi pcb: aspect ratio ≤1:1 per IPC-6016.

- Back-drill via stubs to ≤5mil for signals ≥10Gbps (reduces reflection by 40%).

- Use via-in-pad with solder mask for BGA components (pad diameter = via diameter + 0.2mm).

Via Placement Best Practices

- Place ground vias within 20mil of signal vias (reduces loop inductance by 60%).

- Limit 4 vias per differential pair (each via adds ~1.2nH inductance).

- Avoid via clusters—space vias ≥15mil to prevent plane voids.

3W Rule & Trace Separation: Crosstalk Mitigation

3W Rule Implementation

- Maintain trace spacing = 3x trace width (e.g., 12mil spacing for 4mil width).

- Increase to 5W for ultra low loss pcb (Df ≤0.001) to counteract sensitive signals.

- Apply 2W rule in bottlenecks (BGA breakout) but revert to 3W immediately after.

Additional Isolation Techniques

- Use guard traces (50Ω) between high-speed and analog signals (spacing ≥10mil).

- Route orthogonal traces on adjacent layers to reduce capacitive coupling by 70%.

- For hdi circuit boards, separate digital and analog layers with a ground plane.

Avoid 90-Degree Bends: Signal Continuity

Bend Design Standards

- Use 45-degree bends or curved traces (radius ≥3x trace width).

- 90-degree bends cause 5Ω impedance discontinuity and signal reflection.

- Compensate inner bends in differential pairs (add 2mil length) to maintain symmetry.

Trace Routing Nuances

- Keep trace length ≤λ/20 (λ = signal wavelength) to avoid transmission line effects.

- Minimize stub length ≤10mil (critical for signals ≥25Gbps).

- Use serpentine tuning (pitch ≥5x trace width) for length matching.

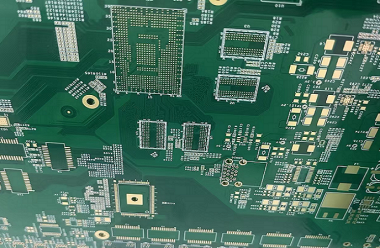

Component Placement: Signal Path Optimization

Placement Guidelines

- Locate high-speed ICs (e.g., SerDes transceivers) within 50mm of connectors.

- Place decoupling capacitors ≤0.5cm from IC power pins (0402/0201 packages).

- Group functional blocks (PLL, RF front-end) to minimize trace length.

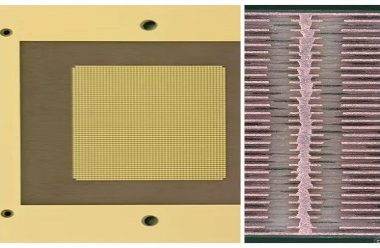

HDI PCB-Specific Placement

- BGA components with ≤0.8mm pitch require microvia fanout (0.15mm vias).

- Space components ≥0.3mm from board edges to prevent impedance variation.

- For 12-layer hdi pcb, place critical components on outer layers (L1/L12).

Signal Integrity and Power Management

SI Optimization Techniques

- Terminate transmission lines: series (50Ω) at source, parallel (100Ω) at load.

- Limit jitter to ≤10% of bit period (e.g., 40ps for 25Gbps signals).

- Use eye diagram analysis to validate signal quality (eye height ≥0.3Vpp).

PI Enhancement

- Design power delivery network (PDN) with impedance ≤0.1Ω at 100MHz.

- Distribute decoupling capacitors (0.1μF + 10μF) every 2cm on power planes.

- For ultra low loss pcb, use low-ESR capacitors (≤5mΩ) to reduce noise.

Decoupling Capacitors & Plane Coupling

Capacitor Selection & Placement

- Use COG/NPO capacitors (±30ppm/°C) for high frequency decoupling.

- Place 0.01μF capacitors within 2mm of IC power pins (ESL ≤1nH).

- Parallel capacitors of different values to cover 1MHz–1GHz frequency range.

Plane Coupling Reduction

- Apply 20H rule: power plane ≤20x dielectric thickness smaller than ground plane.

- For hdi pcb, use embedded capacitance materials (εr ≥10) between planes.

- Maintain 1mm clearance between power planes and board edges to reduce fringing fields.

Simulation: Pre-Manufacturing Validation

Mandatory Simulations

- SI simulation: crosstalk, reflection, and eye diagram analysis (HyperLynx, SIwave).

- PI simulation: voltage drop (≤5% of supply voltage) and ground bounce (≤100mV).

- EMI simulation: radiated emissions (≤30dBμV/m per CISPR 22).

Simulation-Driven Iteration

- Adjust trace spacing if crosstalk exceeds -25dB.

- Modify decoupling capacitor values if PDN impedance >0.1Ω.

- Validate via design with 3D field solvers for signals ≥50Gbps.

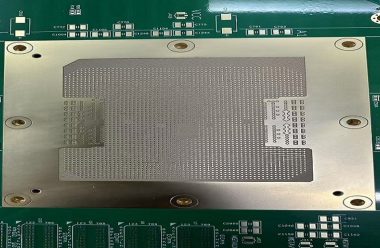

Case Study: 16-Layer HDI Ultra Low Loss PCB

Project Specifications

- Layers: 16 (4+8+4 stackup), data rate: 50Gbps (NRZ), material: Rogers RO4350B (Df=0.0037 @10GHz).

- Impedance targets: 50Ω (single-ended), 100Ω (differential), tolerance ±3%.

- Components: 0.5mm pitch BGA (2400 pins), hdi circuit boards with stacked microvias.

Issues Encountered

- Crosstalk (+15dB) between adjacent differential pairs (spacing = 2x width).

- Via stub reflections causing eye closure (stub length = 15mil).

- Ground bounce (150mV) due to inadequate decoupling.

Improvements Implemented

- Increased pair spacing to 3x width (-32dB crosstalk).

- Back-drilled vias to 3mil stub length (reflection loss ≤-20dB).

- Added 0.1μF decoupling capacitors every 1.5cm (ground bounce ≤80mV).

Results

- Signal integrity compliance (eye height = 0.4Vpp, jitter = 35ps).

- Manufacturing yield: 98.2% (up from 82% initial).

- EMI emissions: 28dBμV/m (meets CISPR 22 Class B).

| Case Study Aspect | Details / Parameters |

|---|---|

| Project Specifications |

• Layers: 16 (4+8+4 stackup) • Data rate: 50Gbps (NRZ) • Material: Rogers RO4350B (Df=0.0037 @10GHz) • Impedance targets: 50Ω (single-ended), 100Ω (differential) ±3% • Components: 0.5mm pitch BGA (2400 pins) with stacked microvias |

| Issues Encountered |

• Crosstalk (+15dB): Adjacent differential pairs (spacing = 2x width) • Via stub reflections: Stub length = 15mil (eye closure) • Ground bounce: 150mV (inadequate decoupling) |

| Improvements Implemented |

• Increased pair spacing to 3x width (-32dB crosstalk) • Back-drilled vias to 3mil stub length (reflection loss ≤-20dB) • Added 0.1μF decoupling capacitors every 1.5cm (ground bounce ≤80mV) |

| Final Results |

• Signal integrity: Eye height = 0.4Vpp, jitter = 35ps • Manufacturing yield: 98.2% (up from 82%) • EMI emissions: 28dBμV/m (CISPR 22 Class B compliant) |

Common Design Errors

- Inadequate Plane Continuity: Splitting ground planes under differential pairs increases crosstalk by 15x—factory rework requires copper filling (cost +$0.50/board).

- Overlooking Via Parasitics: Using through-hole vias (0.3mm diameter) for 25Gbps signals adds 2nH inductance—causes 10% bit error rate.

- Imprecise Length Matching: Differential pair mismatch >10mil leads to skew >50ps—fails compliance for 10Gbps signals.

- Poor Decoupling Placement: Capacitors >1cm from IC pins increase power noise by 3x—requires redesign of power planes.

FAQ

Q1: What’s the difference between Low Loss PCB and ultra low loss pcb for high speed routing?

A1: Low Loss PCB (Df=0.004–0.009 @10GHz) works for 5–25Gbps, while ultra low loss pcb (Df≤0.004) supports ≥25Gbps. Ultra low loss options (e.g., Megtron 7) reduce insertion loss by 40% at 50GHz.

| Material Type | Df (@10GHz) | Supported Data Rate | Key Benefit |

|---|---|---|---|

| Low Loss PCB | 0.004–0.009 | 5–25Gbps | Cost-effective for mid-speed applications |

| Ultra Low Loss PCB | ≤0.004 | ≥25Gbps | 40% lower insertion loss at 50GHz (e.g., Megtron 7) |

Q2: How to implement the 3W rule in dense hdi pcb layouts?

A2: Use 2W rule in BGA breakout (minimum 8mil spacing for 4mil traces) and expand to 3W immediately after. For critical signals, add guard traces to maintain isolation.

Q3: What via type is best for high speed pcb routing?

A3: Microvias (0.1–0.15mm) with back-drilling are optimal—they reduce parasitic inductance by 70% compared to through-hole vias. For hdi circuit boards, stacked microvias (1+2+1 structure) enable dense routing.

Q4: How to validate controlled impedance before manufacturing?

A4: Request impedance coupons from fabricators (100mm trace length) and test with TDR. Ensure tolerance ±5% for high speed pcb; use simulation to adjust trace width if off-target (e.g., +1mil width = -3Ω impedance).

If you need high speed PCB manufacturing or design support,our engineering team provides free DFM analysis and quotation.

![Understanding PCB Costs & Pricing [Your Complete Guide] Understanding PCB Costs & Pricing [Your Complete Guide]](https://hdicircuitboard.com/wp-content/uploads/elementor/thumbs/Understanding-PCB-Costs-Pricing-Your-Complete-Guide-qzzhe6mcaxuolkux3xalfktgavumi9y1aqfbs9bpv4.webp)